# 컴퓨터구조(공영호)

Lee Jun Hyeok (wnsx0000@gmail.com)

February 13, 2025

## 목차

|            |                     |           |

|------------|---------------------|-----------|

| <b>I</b>   | <b><u>서론</u></b>    | <b>3</b>  |

| 1          | 서론                  | 3         |

| 1.1        | 서론                  | 3         |

| 1.2        | 컴퓨터                 | 4         |

| 1.3        | 프로세서의 발전            | 5         |

| 2          | 성능                  | 6         |

| 2.1        | 성능                  | 7         |

| 2.2        | clock               | 7         |

| 2.3        | MIPS                | 10        |

| 2.4        | 벤치마크                | 10        |

| 2.5        | 성능 향상 반영 방법         | 11        |

| <b>II</b>  | <b><u>수의 처리</u></b> | <b>11</b> |

| 1          | 정수의 처리              | 11        |

| 1.1        | 정보의 저장              | 11        |

| 1.2        | unsigned            | 12        |

| 1.3        | signed              | 12        |

| 1.4        | 정수의 연산              | 13        |

| 2          | 실수의 처리              | 14        |

| 2.1        | 실수 표현법              | 14        |

| 2.2        | 고정소수점               | 14        |

| 2.3        | 부동소수점               | 14        |

| <b>III</b> | <b><u>ISA</u></b>   | <b>17</b> |

| 1          | <b>ISA</b>          | <b>17</b> |

| 1.1        | cpu와 어셈블리어          | 17        |

| 1.2        | ISA                 | 18        |

| 2          | <b>RISC-V</b>       | <b>19</b> |

| 2.1        | RISC-V              | 19        |

| 3          | <b>RISC-V 연산</b>    | <b>20</b> |

| 3.1        | 연산과 데이터             | 21        |

|           |                                  |           |

|-----------|----------------------------------|-----------|

| 3.2       | 산술/논리 연산 . . . . .               | 22        |

| 3.3       | 데이터 이동 연산 . . . . .              | 24        |

| 3.4       | 분기 연산 . . . . .                  | 24        |

| 3.5       | Pseudo-instructions . . . . .    | 26        |

| <b>4</b>  | <b>Instruction format</b>        | <b>26</b> |

| 4.1       | Immediate의 저장과 적용 . . . . .      | 26        |

| 4.2       | Instruction format . . . . .     | 27        |

| <b>5</b>  | <b>조건문과 반복문</b>                  | <b>30</b> |

| 5.1       | 조건문 . . . . .                    | 31        |

| 5.2       | 반복문 . . . . .                    | 31        |

| <b>6</b>  | <b>프로시저</b>                      | <b>32</b> |

| 6.1       | 프로시저 . . . . .                   | 32        |

| 6.2       | 프로시저의 구현 . . . . .               | 34        |

| <b>IV</b> | <b><i>processor</i></b>          | <b>35</b> |

| <b>1</b>  | <b>datapath</b>                  | <b>35</b> |

| 1.1       | single-cycle processor . . . . . | 35        |

| 1.2       | datapath . . . . .               | 36        |

| 1.3       | 디지털 시스템의 구현 . . . . .            | 36        |

| 1.4       | datapath의 구성요소 . . . . .         | 37        |

| 1.5       | 명령어 실행 과정 . . . . .              | 42        |

| <b>2</b>  | <b>pipeline</b>                  | <b>43</b> |

| 2.1       | pipeline . . . . .               | 43        |

| 2.2       | RISC-V pipeline . . . . .        | 44        |

| 2.3       | structural hazard . . . . .      | 45        |

| 2.4       | data hazard . . . . .            | 46        |

| 2.5       | hazard detection . . . . .       | 47        |

| 2.6       | control hazard . . . . .         | 50        |

| <b>3</b>  | <b>advanced processor</b>        | <b>53</b> |

| 3.1       | advanced processor . . . . .     | 53        |

| <b>V</b>  | <b><u>메모리</u></b>                | <b>54</b> |

| <b>1</b>  | <b>memory</b>                    | <b>54</b> |

| 1.1       | memory . . . . .                 | 54        |

| 1.2       | memory 성능 개선 . . . . .           | 56        |

| 1.3       | memory 요약 . . . . .              | 57        |

| <b>2</b>  | <b>cache</b>                     | <b>59</b> |

| 2.1       | cache . . . . .                  | 59        |

| 2.2       | cache arrangement . . . . .      | 60        |

| 2.3       | direct mapped . . . . .          | 60        |

| 2.4       | fully associative . . . . .      | 63        |

| 2.5       | N-way set associative . . . . .  | 64        |

| 2.6       | cache performance . . . . .      | 65        |

| <b>3</b>  | <b>virtual memory</b>            | <b>67</b> |

| 3.1       | virtual memory . . . . .         | 67        |

| 3.2       | paging . . . . .                 | 68        |

# Part I

## 서론

### 1. 서론

#### 1.1. 서론

##### 1.1.1. 컴퓨터 구조

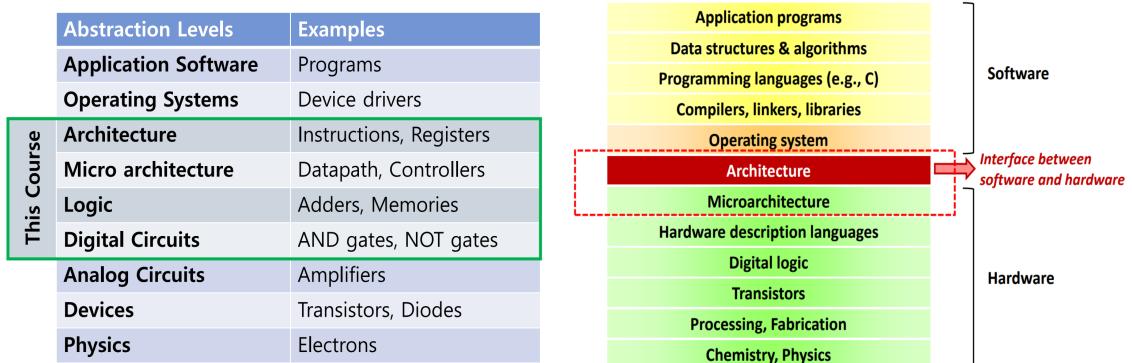

**Definition 1** 컴퓨팅 플랫폼(하드웨어, 인터페이스, 시스템 소프트웨어 등)을 디자인하는 과학/예술을 컴퓨터 구조(Computer Architecture)라고 함.

즉, 성능적/디자인적 목표를 위해 컴퓨터를 더 효율적으로 설계하는 것.

##### 1.1.2. 실행 소프트웨어의 기저

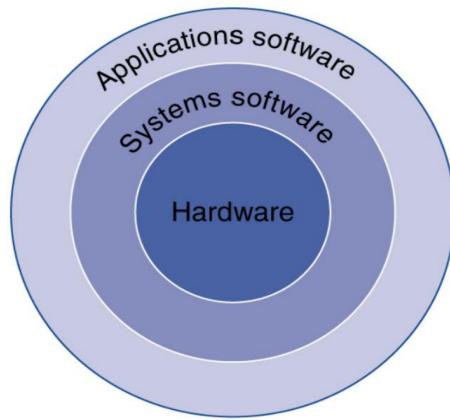

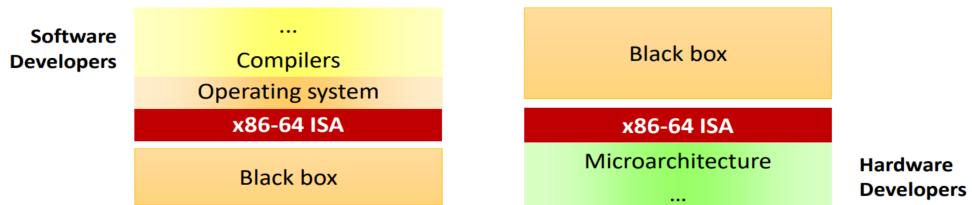

고급 언어를 사용하여 제작한 소프트웨어의 밑에는 컴파일러, 운영체제 등의 시스템 소프트웨어가 있음. 또 그 밑에는 프로세서, 메모리, I/O 컨트롤러 등을 포함하는 하드웨어가 있음.

추상화되어 있는 고급 지식들은 복잡한 저급 지식을 몰라도 프로그래밍을 할 수 있도록 하지만, 더 나은 소프트웨어를 만들려면 저급 지식을 알 필요가 있음. 그렇기에 컴퓨터 구조를 배워야 함.

##### 1.1.3. 학습 내용 개요

본 수업에서는 소프트웨어와 하드웨어 사이의 부분을 어떤 식으로 효율적으로 설계할 것인지를 학습함.

또한, 소프트웨어/하드웨어 개발자 모두에게 사용되는 어셈블리어 같은 인터페이스를 어떻게 디자인할 것인지, 주어진 공간에 트랜지스터를 어떻게 배치할 것인지, 메모리를 어떻게 사용할 것인지 등에 대한 학습을 함.

## 1.2. 컴퓨터

### 1.2.1. 컴퓨터의 종류

컴퓨터는 PC(Personal Computer), 슈퍼컴퓨터, 서버컴퓨터, 임베디드 컴퓨터 등으로 나눌 수 있음.

PC는 다양한 소프트웨어를 구동하기 위해 일반적으로 사용되는 컴퓨터로, 비용/성능 면에서의 균형이 잘 조율되어 있음.

슈퍼컴퓨터는 과학/수학적 계산을 위한 하이엔드 컴퓨터로, 높은 성능을 가지고 있지만 전반적 컴퓨터 시장에서의 입지는 작음.

서버컴퓨터는 서버, 데이터센터로서 사용되는 컴퓨터로, 높은 성능과 안정성을 가지고 있고 그 규모가 큼.

임베디드 컴퓨터는 자동차, 기계, 가전제품 등에 들어가는 컴퓨터로, 엄격한 성능/비용적 제한을 만족시킴.

### 1.2.2. 폰 노이만 아키텍처

**Definition 2** 폰 노이만 아키텍처(Von Neumann Architecture)는 최초의 컴퓨터 구조이면서 현대 컴퓨터의 기본적인 형태를 결정한 아키텍처임.

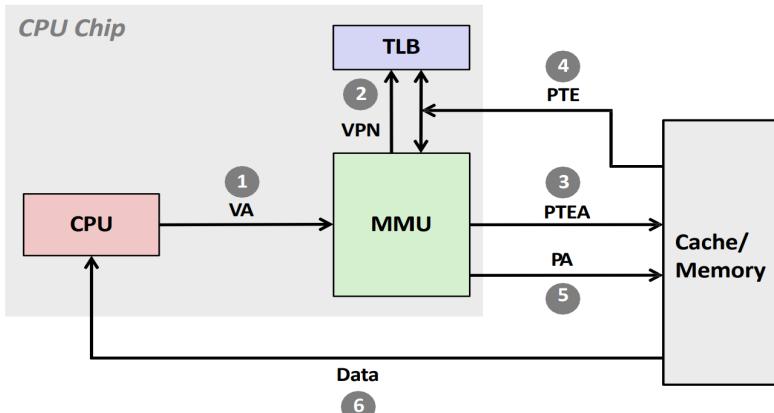

폰 노이만 아키텍처는 *cpu-memory*의 구성을 가짐. *cpu*가 메모리에 주소를 주면 메모리에서 해당 주소에 있는 명령어를 *cpu*로 전달하고 *cpu*는 명령을 전달된 명령을 수행함.

### 1.2.3. 컴퓨터의 물리적 구조

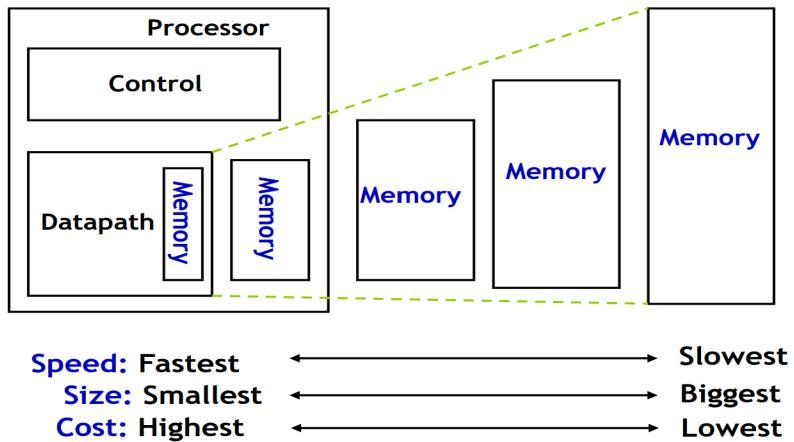

폰 노이만 아키텍처를 따르는 컴퓨터들은 기본적으로 CPU(Central Processing Unit), Memory, I/O들로 구성되어 있음. 또한 CPU는 control과 datapath로 구성됨.

본 수업에서는 CPU, Memory, 그리고 I/O 중 저장장치인 HDD와 SSD에 대해 공부함.

### 1.2.4. 마이크로프로세서

**Definition 3** 마이크로프로세서(Microprocessor)는 작은 반도체 칩으로 만들어진 프로세싱 유닛으로, 컴퓨터 프로그램의 연산을 수행하기 위한 논리적 전기 회로를 가지고 있음.

*n*비트 프로세서라고 할 때의 이 비트는 한 번에 처리할 수 있는 데이터의 처리량, 레지스터의 크기를 의미함. *cpu*는 4비트, 8비트, 16비트, 32비트, 64비트 순으로 발전되어 왔음. 32비트/64비트 운영체제는

32비트/64비트 프로세서가 있기에 존재할 수 있는 것.

마이크로프로세서는 cpu, gpu, npu 등을 포괄하는 개념임. cpu는 컴퓨터의 메인 처리 마이크로프로세서이고, gpu는 그래픽 처리에 특화된 마이크로프로세서, npu는 gpu에서 그래픽 처리 기능을 제외하고 ai 개발에 특화된 마이크로프로세서임. 참고로, gpu와 npu는 모두 cpu로부터 만들어졌음.

각 마이크로프로세서별로 사용하는 언어와 작동 방식이 다름.

예를 들어, Intel x86, ARM, MIPS 등이 있음.

### 1.2.5. cisc와 risc

**Definition 4** 1. *cisc*

*cisc*(complex instruction set computer) 명령어 개수가 많고 복잡한 작업을 가지는 아키텍처임.

코드 길이가 짧지만 명령어 별로 수행하는 작업이 복잡함. 적은 수의 명령어로 작업을 수행할 수 있어 컴파일러 구현에는 유리함.

2. *risc*

*risc*(reduced instruction set computer)는 명령어 개수가 적고 비교적 단순한 작업을 가지는 아키텍처임.

*risc*은 register 기반 명령어들을 가짐. 각 명령어들은 고정된 크기를 가지고, 메모리 접근에는 *load/store* 명령어만을 사용함. 또한 *flag*를 사용하는 조건부 코드가 없음.

*risc*은 작업 수행 시에 더 많은 명령어를 수행해야 하고 그에 따라 더 시간이 오래 걸릴 수 있지만, 최적화, 낮은 전력 소모, 낮은 가격, 작고 빠른 하드웨어에서의 실행에 있어 유리하기 때문에 임베디드 등에서 자주 사용됨.

ARM, RISC-V, MIPS, IBM PowerPC 등에서 사용함.

하드웨어를 업그레이드하면 성능은 충분히 보장되기 때문에, cisc와 risc의 선택에는 코드 호환성이 주된 지표로 기능함.

실제로는 cisc와 risc의 특성을 잘 조합하여 만든 cpu들이 존재함.

## 1.3. 프로세서의 발전

### 1.3.1. 무어의 법칙

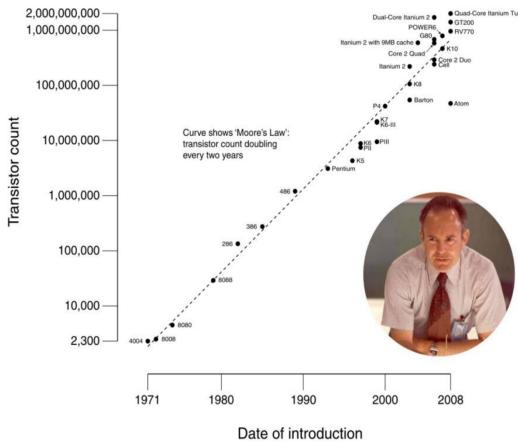

**Definition 5** 18 또는 24개월마다 반도체에 들어가는 단위 면적당 트랜지스터의 개수가 2배가 될 것이라는 것이 무어의 법칙(Moore's Law)으로 불리는 무어의 발언임.

컴퓨터 구조에서 가장 유명한 법칙 중 하나.

cpu는 트랜지스터를 이용한 논리회로로 구성되어 있음. 트랜지스터가 많아지면 한 번에 처리할 수 있는 처리량이 늘어나고, 성능이 높아짐. 다만 이에 따라 발열이 심해짐.

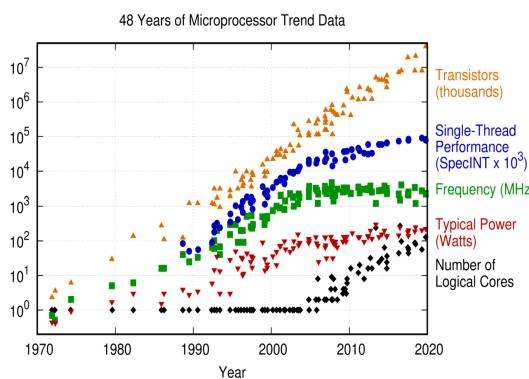

이 법칙이 2000년대 초반까지는 나름 잘 들어맞다가, 단위면적당 전력소모량이 많아짐에 따라 발열이 심해지는 등의 한계에 봉착하여 현재는 그 증가폭이 더뎌진 상황.

CPU Transistor Counts 1971-2008 & Moore's Law

### 1.3.2. 병렬화

**Definition 6** 병렬화(Parallelism)를 통해 프로세서의 발전이 이루어졌음. 병렬화는 명령어 레벨의 병렬화(ILP, Instruction Level Parallelism), 데이터 레벨의 병렬화(DLP, Data Level Parallelism), 작업 레벨의 병렬화(TLP, Task Level Parallelism)로 나눌 수 있음.

ILP는 명령어 수행에서의 병렬화, DLP는 하나의 명령어에 여러 개의 데이터를 실어서 처리하는 병렬화, TLP는 스레드를 늘리는 등 여러 작업을 동시에 수행하는 병렬화를 말함.

특히 DLP와 TLP는 gpu의 발전을 가속화시켰음. gpu는 많은 양의 데이터를 빠르게 처리할 수 있어야 하기 때문.

각 병렬화에 대한 내용은 뒤에서 자세히 다를 예정.

### 1.3.3. 멀티코어로의 전환

트렌지스터의 개수가 늘어나며 단위면적당 전력소모량이 많아짐에 따라 발열이 심해져 파워의 한계(typical power)로 single-Thread의 성능 증가가 더뎌지는 지점을 마주하게 됨. 코어와 스레드를 여러 개 사용하는 멀티코어로의 전환은 이런 문제점의 해결책으로서 등장했음.

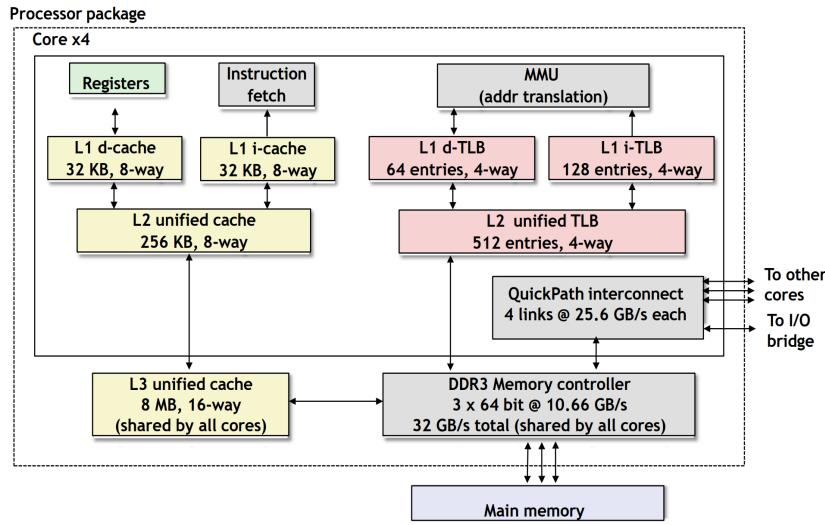

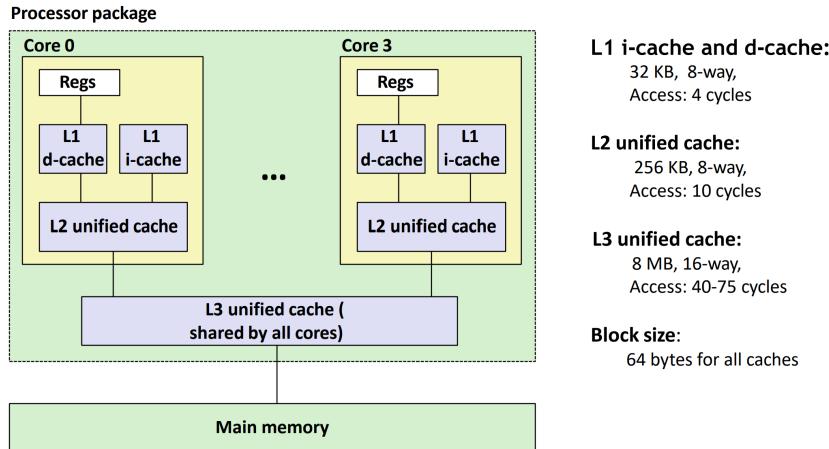

캐시 메모리 등도 증가했는데, 자세한 내용은 나중에 다름.

## 2. 성능

추후에 계산 연습도 하자.

## 2.1. 성능

### 2.1.1. 성능

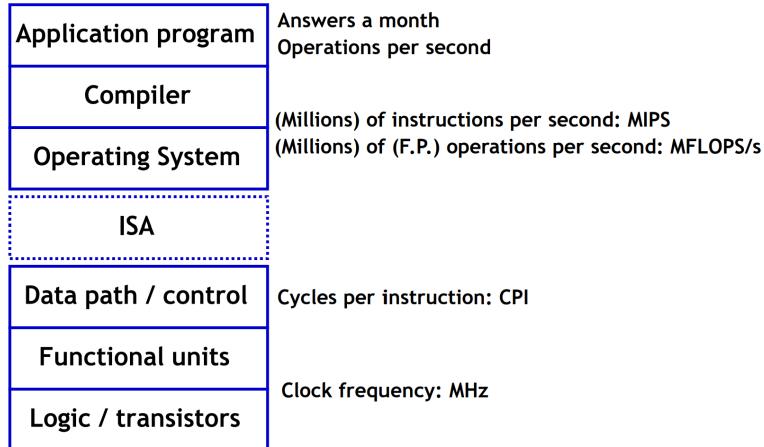

컴퓨터에서의 성능은 프로세서 성능, HDD/SSD 성능, 메모리 크기, 그래픽, 전력 소모량, 가격, 무게 등으로 생각해 볼 수 있지만, 대부분의 성능 평가 기준은 시간임. 대체로 속도가 곧 성능인 것. 아래는 계층별 성능 척도임.

### 2.1.2. cpu 성능

**Definition 7** *cpu*의 성능은 실행 시간의 역수로 나타냄.

$$\text{Performance} = 1 / \text{Execution\_time}$$

즉, 시간이 줄어들면 성능이 좋아지는 것.

두 cpu 사이의 성능 차이는  $\text{Performance}_1 / \text{Performance}_2$ 로 계산이 가능함.

## 2.2. clock

### 2.2.1. clock

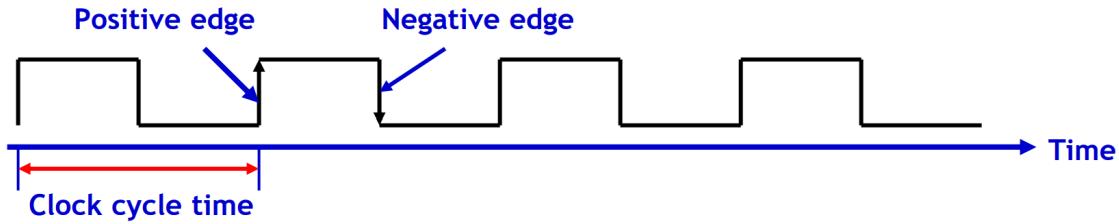

**Definition 8** *cpu*에서는 *clock*으로 시간을 측정함.

*cpu*내에 있는 클록 펄스(*clock pulse*)를 기준으로 *clock cycle time*(클럭 주기)과 *clock rate*(클럭 속도, 클럭 주파수, *clock frequency*) 값을 계산하고, 이를 통해 시간을 측정하는 것.

클록 펄스는 수정 발진자(*crystal oscillator*) 등의 규칙적인 진동에 의해 발생하는 일정한 간격을 갖는 전자적 펄스를 말함. 이 펄스의 움직임을 그림으로 나타내면 아래와 같고, 신호가 올라가는 지점을 *positive edge*, 내려가는 지점을 *negative edge*라고 함.

*clock cycle time*은 *clock* 신호가 0에서 1로 갔다가 다시 0으로 변하는 데 걸리는 시간임. (*positive/negative edge*에서 *positive/negative edge* 사이의 시간 간격.) 단위로는 ns(나노초) 등을 사용함.

*clock rate*는 *clock cycle time*의 역수로, 1초 동안 *clock* 신호가 몇 번 바뀌는지를 나타냄. 단위로는 Hz(헤르츠), MHz, Ghz, cycles/sec 등을 사용함.

즉, 컴퓨터에서는 *clock*으로 어떤 작업의 객관적인 시간을 측정함.

*clock* 신호는 아날로그 값으로부터 온 것으로, 실제로 각진 그래프의 데이터를 가지지는 않음. 지정한 기준 점을 넘느냐 안 넘느냐로 그래프를 그린 것.

참고로, 기가, 메가, 킬로, 나노, 마이크로 등 물리학에서의 단위 체계는 필수 소양이라고 하심. 10의 지수가 12(테라, T), 9(기가, G), 6(메가, M), 3(킬로, k), -3(밀리, m), -6(마이크로,  $\mu$ ), -9(나노, n)인 것들은 제대로 외우자.

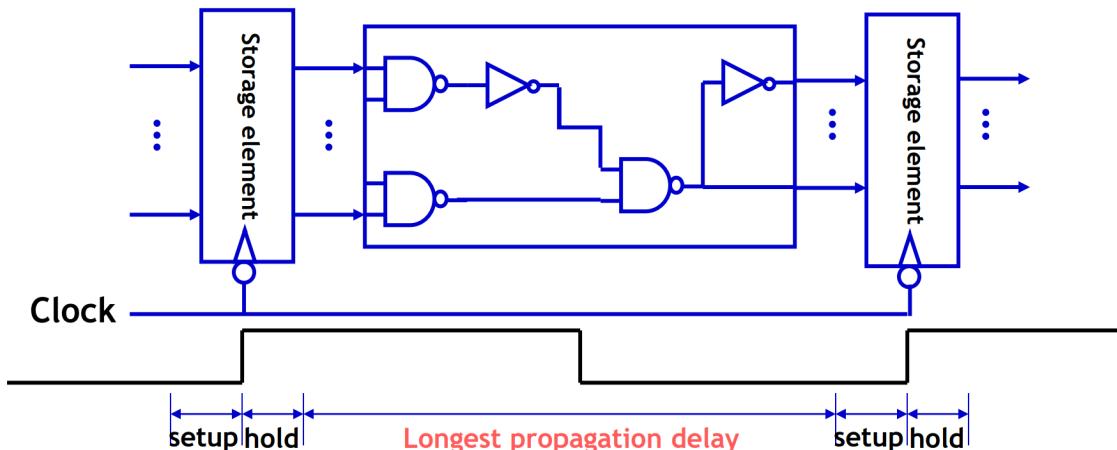

### 2.2.2. 전파 지연 시간

**Definition 9** 마이크로프로세서 내부 대부분의 회로는 하나의 clock 신호에 대해 동기화되는데, 이때 프로세서 내부에 있는 모든 회로가 다 동작할 수 있을 만큼 clock이 느려야 정상적으로 동작함. 이때 프로세서 내 회로 중 시간적으로 가장 먼 경로를 *Critical Path*라고 함.

이때 *Critical Path*에서 걸리는 시간을 전파 지연 시간(*Longest Propagation Delay, Critical Path Delay*)라고 함.

마이크로프로세서의 clock cycle time의 지정은 프로세서의 회로와 연관이 있음. 프로세서에서는 clock에 적절히 맞추어 데이터를 송수신하기에, 각 장치들이 데이터를 안정적으로 주고받기 위해서는 동기화된 clock 신호를 가지고 있어야 함. 장치별로 성능에 따라 데이터를 수신받는 속도가 다르기 때문에, 시간적으로 가장 먼 거리까지 송수신이 될 정도로 clock이 느려야 하는 것임.

storage element 사이의 회로가 길고 복잡할수록 Critical Path Delay가 늘어남.

아래의 그림에서 setup time과 hold time은 1과 0 신호 사이의 변화하는 시간을 의미함. setup time은 1로 가는 시간, hold time은 0으로 가는 시간.

여담으로 intel의 cpu는 storage element(레지스터, 캐시)를 회로 중간에 심어 Critical Path Delay를 줄임. 다만 그러면 비용이 많이 들어감.

### 2.2.3. 실행시간 측정

**Definition 10** *clock*(cpu의 실행 시간)으로 프로그램의 실행 시간을 측정할 수 있음. 즉, 실행 시간을 아래의 식으로 구할 수 있음. 물론 *Clock\_cycle\_time*(주기) 대신 *Clock\_rate*(진동수)를 사용할 수도 있음.

$$\text{Execution\_time} = \text{Clock\_cycles\_for\_program} * \text{Clock\_cycle\_time}$$

하지만 아키텍처, 프로세서마다 clock이 다를 수 있기 때문에(ex. single cycle vs. multi cycle) 실행 시간을 이렇게 구하면 직관적이지 않음. 그래서 CPI를 활용하여 표기함.

### 2.2.4. CPI를 활용한 표기

**Definition 11** instruction 당 clock cycle을 CPI(Cycles per Instruction)라고 함. 즉, 실행 시간을 아래의 식으로 구할 수 있음. 물론 CPI의 역수인 IPC(Instructions per Cycle)를 사용할 수도 있음.

$$\text{Execution\_time} = \#_{\text{of\_Instructions}} * \text{CPI} * \text{Clock\_cycle\_time}$$

instruction마다의 clock cycle을 구하고 그 평균값을 CPI로 사용함. instruction마다의 clock cycle(각각의 CPI)을 고려하면 전체 cycle 수는 아래와 같으므로 평균 CPI를 구할 수 있음. 평균 CPI를 반영하면 실행 시간도 간단히 구할 수 있음.

$$\begin{aligned}\text{Average\_CPI} &= ((\text{CPI}_1 * \#_{\text{of\_In\_1}}) + \dots + (\text{CPI}_n * \#_{\text{of\_In\_n}})) \\ &\quad / \#_{\text{of\_Instructions}} \\ \text{Execution\_time} &= ((\text{CPI}_1 * \#_{\text{of\_In\_1}}) + \dots + (\text{CPI}_n * \#_{\text{of\_In\_n}})) \\ &\quad * \text{Clock\_cycle\_time}\end{aligned}$$

이때 하나의 프로세서 내에서 명령어 별로 다른 cycle 수를 가지고 있을 수 있기 때문에, CPI 값을 instruction들의 평균으로 지정해야 함.

서로 다른 IPA의 비교를 위해 CPI를 사용할 수 있음. 물론 CPI가 언제나 정확한 지표로서 기능하지는 않음.

Instruction의 개수, CPI, clock cycle time을 줄여서 성능을 개선(시간 단축)할 수 있음. 디자이너는 여러 tradeoff를 잘 고려해서 instruction, cycle 수 등을 설계함.

ex. 프로그램에 사용된 instruction의 비율이 아래와 같을 때, 평균 CPI(그냥 CPI로 표기)와 실행 시간은 아래와 같음.

$$\text{CPI} = 0.43 * 1 + 0.21 * 2 + 0.12 * 2 + 0.24 * 2 = 1.57$$

$$\text{Execution\_time} = \#_{\text{of\_Instructions}} * 1.57 * \text{Clock\_cycle\_time}$$

| Instruction Class | Frequency | CPI <sub>i</sub> |

|-------------------|-----------|------------------|

| ALU operations    | 43%       | 1                |

| Loads             | 21%       | 2                |

| Stores            | 12%       | 2                |

| Branches          | 24%       | 2                |

## 2.2.5. 계층별 성능 개선

clock의 관점에서, 아래와 같이 계층별로 영향을 미칠 수 있는 개선점이 다름.

이때 organization은 프로세서 구성을, technology는 하드웨어적인 기술을 말함.

코드를 개선하거나 좋은 컴파일러를 사용하면 instruction 수를 줄일 수 있음.

CPI와 Clock rate는 하드웨어적인 부분에서 주로 개선을 할 수 있음. 즉, 소프트웨어만 고려한 성능의 개선에는 한계가 존재함. (ex. OpenAI의 칩 개발 시작)

|              | Instruction count | CPI | Clock rate |

|--------------|-------------------|-----|------------|

| Program      | v                 |     |            |

| Compiler     | v                 |     |            |

| ISA          | v                 | v   |            |

| Organization |                   | v   | v          |

| Technology   |                   |     | v          |

## 2.3. MIPS

clock이 시간을 기준으로 성능을 평가했다면, MIPS는 instruction 처리량을 기준으로 성능을 평가함.

### 2.3.1. MIPS

**Definition 12** MIPS(Million Instructions per Second)는 초당 instruction 처리량으로 성능을 나타내는 지표임. MIPS는 아래와 같이 구함.

$$\text{MIPS} = \text{Instruction\_count} / (\text{Execution\_time} * 10^6)$$

이때 시간은 clock으로 구할 수 있음.

MIPS는 초당 실제 처리 instruction 개수가 아니라  $10^6$ 으로 나눈 개수임. 예를 들어 MIPS가 350이면 350 million(백만) 개의 instruction을 처리한 것. 당연히 데이터가 백만 단위로 주어지면  $10^6$ 으로 나눠줄 필요 없음.

clock을 짧을수록, MIPS는 클수록 빠른 것.

MIPS는 instruction set을 고려하지 않아 정확하지 않을 수 있음. CISC와 RISC를 생각하면 당연함.

### 2.3.2. MFLOPS

**Definition 13** MFLOPS(Million Floating-point Operations per Second)는 초당 부동소수점 연산(부동소수점 덧셈/곱셈/뺄셈 등) 처리량으로 성능을 나타내는 지표임.

주로 부동소수점 곱셈을 사용함.

### 2.3.3. 연산 표기

ALU는 산술 연산을, load는 데이터를 가져오는 연산을, stroe는 저장 연산을, branch는 분기 연산을 의미함. 이때 ALU는 내부 회로만 사용하여 빠르지만, load, store는 메모리에 접근하기 때문에 느림. branch는 조건 분기 때문에 느림.

## 2.4. 벤치마크

### 2.4.1. 벤치마크

**Definition 14** 성능을 시험하여 수치화한 것을 벤치마크(Benchmark)라고 함. 특정 instruction 집합이나 코드를 이용해 테스트하고, 여러 가지 지표를 종합하여 점수로 나타내는 것.

시뮬레이션을 위해 사용되는 이런 instruction 집합이나 코드를 워크로드라고 함.

### 2.4.2. 벤치마크의 요건

벤치마크가 제대로 된 점수로서 기능하려면 아래의 요건들을 만족해야 함.

Relevant: 타겟 시스템 (e.g., 모바일, 서버)에서 실제로 수행될 법한 워크로드를 사용해야 함.

Understandable: 결과를 쉽게 이해할 수 있어야 함.

Good Metric(s): 알아보기 쉽게 표기해야 함. 사용자들은 보통 점수를 선호함.

Scalable: 시스템 또는 어플리케이션이 달라져도 사용할 수 있어야 함.

Coverage: 타겟 시스템에서 중요한 것을 Oversimplify하지 않아야 함.

Acceptance: 판매자와 사용자 모두 납득할 수 있어야 함.

## 2.5. 성능 향상 반영 방법

### 2.5.1. Amdahl's Law

**Definition 15** 실행시간의 향상은 1. 얼마나 향상되었는지 2. 향상된 부분이 전체에 얼마나 영향을 끼쳤는지에 의해 결정된다는 법칙을 *Amdahl's Law*(암달의 법칙)라고 함. 이를 반영한 식은 아래와 같음.

```

New_time = Old_time * ((1 - Fraction) + (Fraction / Enhanced_degree))

```

Amdahl's law는 무어의 법칙과 더불어 가장 중요한 법칙 중 하나임.

즉, 어떤 부분이 향상되었으면, 해당 부분이 전체에서 차지하는 비율만큼 반영해주는 것. 예를 들어, 10%에 해당되는 연산의 성능이 2배 향상되었으면 개선된 전체 실행 시간은  $New\_time = Old\_time * (0.9 * (0.1 / 2))$ 로 구할 수 있음.

## Part II

# 수의 처리

## 1. 정수의 처리

### 1.1. 정보의 저장

#### 1.1.1. 정보의 저장

컴퓨터에서 정보는 여러 개의 비트와 자료형으로 구성됨. 이진 숫자로 정보를 표현하는데, 자료형이 그 표현과 해석의 기준이 되는 것.

#### 1.1.2. 바이트 단위 인코딩

메모리는 바이트 단위로 주소가 부여되기 때문에 바이트 단위로 정보를 표기하는 것이 편리함. 이진수, 8진수, 16진수로 주로 표현하고, 10진수도 사용은 가능함. 각 진법은 환경별로 다르게 구분하지만, 대체로 0b, 0, 0x 등으로 구분함.

1바이트는 진법별로 아래와 같이 표기함.

Binary : 00000000 ~ 11111111

Octal : 000 ~ 888

Decimal : 0 ~ 255

Hexadecimal : 00 ~ FF

16진수를 주로 사용함.

## 1.2. `unsigned`

### 1.2.1. `unsigned`

`unsigned` 정수는 단순히 이진수로 바꾸어 저장함.

## 1.3. `signed`

### 1.3.1. 부호비트의 사용

`signed` 정수는 부호 비트(sign bit)를 사용해 부호를 표기함. 주로 최상위 비트(가장 왼쪽 비트)가 부호 비트로 사용됨. 양수는 부호 비트가 0, 음수는 부호 비트가 1임. `unsigned`와의 유사성을 지키기 위해 양수가 0, 음수가 1인 것.

부호 비트(최상위 비트)는 MSB(most significant bit)라고도 함. 가장 중요한 비트. 최하위 비트는 LSB(least significant bit)라고도 함.

양수는 `unsigned`와 같이 표기하면 되는데, 음수는 부호-크기 표현, 1의 보수, 2의 보수 등 방법이 여러 가지임. 물론 현대의 대부분의 컴퓨터에서는 2의 보수를 사용함.

### 1.3.2. 부호-크기 표현

**Definition 16** 첫번째 비트로 부호를 표기하고, 나머지 비트로 수를 표기하는 방법을 **부호-크기 표현** (*Sign-magnitude Representation*)이라고 함.

0을 표현하는 방법이 00...0과 10...0 두 가지이므로 불완전함.

부동소수점 연산에서는 이 방법을 사용하지만 정수에서는 사용하지 않음.

ex. 3은 0011, -3은 1011

### 1.3.3. 1의 보수

**Definition 17** 비트를 전부 뒤집(NOT 연산)했을 때 양수와 음수가 대응되도록 표기하는 방법을 **1의 보수 표현** (*One's Complement Representation*)이라고 함.

0을 표현하는 방법이 00...0과 11...1 두 가지이므로 불완전함.

당연하게도 1의 보수에서도 부호비트가 존재함.

여기서 보수는 뒤집어 표현하는 것을 말함.

ex. 3은 0011, -3은 1100.

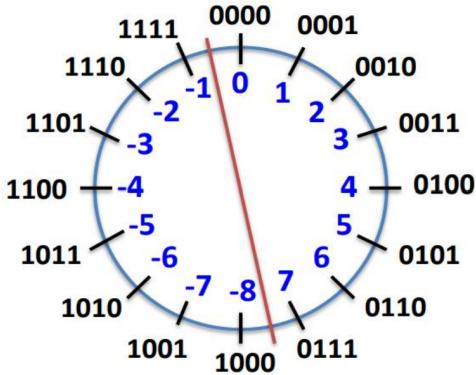

### 1.3.4. 2의 보수

**Definition 18** 비트를 전부 뒤집(NOT 연산)하고 1을 더했을 때 양수와 음수가 대응되도록 표기하는 방법을 **2의 보수 표현** (*Two's Complement Representation*)이라고 함.

0이 00...0으로 유일하게 표현됨.

당연하게도 2의 보수에서도 부호비트가 존재함.

비대칭적인 표현 범위를 가지기 때문에 0이 유일하게 표현됨.

현대의 대부분의 컴퓨터에서는 2의 보수를 사용함.

### 1.3.5. Sign Extension

sign 데이터를 더 큰 공간에 저장하면, 부호 비트가 복사되어 왼쪽에 추가됨. 이렇게 늘리면 2의 보수가 제대로 작동함.

ex. 0010은 0000 0010, 1010은 1111 1010.

## 1.4. 정수의 연산

C언어 기반으로 정리함.

### 1.4.1. 비트 연산

&, |, ~, ^로 모든 정수 자료형 데이터에 대한 비트 연산을 할 수 있음.

### 1.4.2. 논리 연산

&&, ||, !로 논리 연산을 할 수 있음.

이때 early termination이 적용되어, 판단이 끝나면 더 이상 판단을 하지 않음.

### 1.4.3. 시프트 연산

«, »로 시프트 연산을 할 수 있음.

오른쪽으로 이동하면 빈 공간에는 0이 채워짐. 왼쪽으로 이동하면 logical shift인 경우 0이, arithmetic shift인 경우 부호 비트가 채워짐.

0보다 작은 수 또는 데이터 길이보다 긴 수 만큼 시프트 연산을 하는 것은 정의되어 있지 않음.

곱셈 연산은 하드웨어적으로 부담이 심하기 때문에, 2의 거듭제곱을 곱하거나 나누는 것을 시프트연산으로 대체할 수 있음.

### 1.4.4. 덧셈/곱셈 연산

실제로 덧셈/곱셈은 이진수끼리 이뤄지는데, 그 방식은 10진수의 덧셈과 동일함. 연산 결과가 overflow된 경우 넘친 값은 무시하면 됨. 물론 그 결과가 주어진 비트로 표현할 수 없는 크기의 수라면 실제 값과는 다른 값으로 overflow됨.

오버플로우가 일어날 수 있음. 이때 signed냐 unsigned냐에 따라 오버플로우된 결과가 다르게 해석됨. 당연하게도 오버플로우는 곱셈에서 더 쉽게 일어남.

컴퓨터구조의 측면에서 보면 부호확장을 우선 하고, 그 이후에 연산을 수행함.

## 2. 실수의 처리

### 2.1. 실수 표현법

#### 2.1.1. 실수 표현법

실수를 표현하는 방식으로는 고정소수점(Fixed-point)과 부동소수점(Floating-point)이 있음.

### 2.2. 고정소수점

#### 2.2.1. 고정소수점

**Definition 19** 고정소수점(Fixed-point) 방식은 소수점 위치를 고정하여 실수를 표현하는 방식임.

정수부와 소수부의 비트 수를 미리 약속한 후 표현함. 이때 정수부는  $n$ 번째 비트의 경우  $2^0$ 의  $n-1$ 승에 해당되고, 소수부는 소수점으로부터  $n$ 번째 비트의 경우  $2^0$ 의  $-n$ 승에 해당됨. 각 자리의 거듭제곱들을 전부 더하면 해당 소수가 되는 것.

정수부와 소수부 비트 사이에 *binary point*(2진 소수점)가 들어감. 이때 *binary point*는 비트 표현에 포함되지 않으므로 해당 위치에 존재한다는 약속만이 존재함.

실수의 표현 시에는 부동소수점이 주로 쓰이지만, 고정소수점도 종종 쓰임.

예를 들어, 6.75는 0110110으로 표현됨. *binary point*를 표기하면 0110.110임.

#### 2.2.2. signed 표현법

**Definition 20** 고정소수점의 *signed* 표현법으로는 부호비트를 사용하는 것(sign-magnitude)과 2의 보수로 표현하는 것이 있음.

부호비트와 2의 보수는 정수에서의 방식과 동일함.

### 2.3. 부동소수점

#### 2.3.1. 부동소수점

**Definition 21** 부동소수점(Floating-point) 방식은 소수점 위치를 가장 큰 자릿수의 숫자 바로 오른쪽으로 고정하여 표현하는 방식임.

소수점 위치를 가장 큰 자릿수의 바로 오른쪽으로 지정하기 위해 특정 수의 거듭제곱을 곱한 형태로 실수를 나타냄. 즉,  $\pm M \times B^E$  꼴로 표현됨. 이때의  $M$ 을 *mantissa*(가수부),  $B$ 를 *base*(밑),  $e$ 를 *exponent*(지수부)라고 함. 이때 가수부는 수의 정밀도와, 지수부는 수의 범위와 관련이 있음.

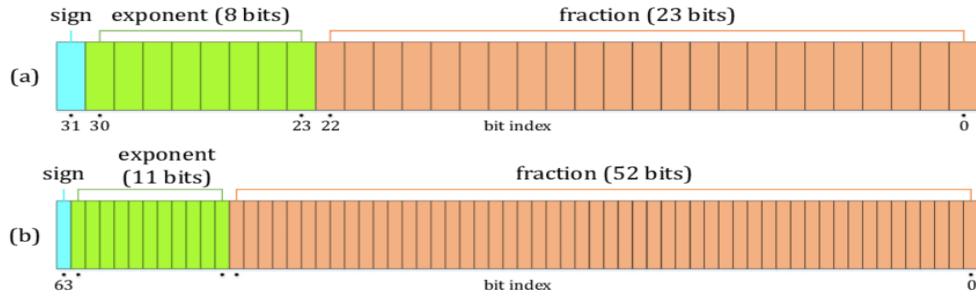

부동소수점 표현 방식은 사용하는 비트 수에 따라 단정밀도와 배정밀도로 나눌 수 있음.

1. 32비트 크기의 부동소수점 표현 방식을 단정밀도(single precision)라고 함. 단정밀도는 1비트의 부호비트, 8비트의 *exponent*, 23비트의 *mantissa*를 가지고, *bias*는 10진수로 127임. *c*에서의 *float*이 단정밀도 방식을 사용함.

2. 64비트 크기의 부동소수점 표현 방식을 배정밀도(double precision)라고 함. 배정밀도는 1비트의 부호비트, 11비트의 *exponent*, 52비트의 *mantissa*를 가지고, *bias*는 10진수로 1023임. *c*에서의 *double*이 단정밀도 방식을 사용함.

부동소수점의 방식은 여러 가지가 있지만, 여기서는 IEEE 754 단정밀도 부동소수점 표현 방식을 정리함.

예를 들어,  $273 = 2.73 \times 10^2$  등으로 나타내는 것임.

부호 비트 1비트, *exponent* 8비트, *fraction* 7비트를 쓰는 google의 *bfloat16*이 존재하는 것처럼, 다양한 부동소수점 표현 방식이 존재함. 이 경우 IEEE 754 단정밀도와 *exponent*의 크기가 같으므로 정밀도는 낮지만

더 적은 비트 수로 동일한 범위의 수를 표현할 수 있음.

### 2.3.2. IEEE 754 단정밀도 부동소수점 표현 방식

**Definition 22** IEEE 754 단정밀도 부동소수점 표현 방식은 단정밀도 공간에 1비트의 부호 비트, 8비트의 exponent값, 23비트의 mantissa값을 저장하지만, 몇 가지 기법들이 추가로 사용됨.

IEEE 754 단정밀도 부동소수점은 아래의 방식으로 실수를 표현함. base는 2를 사용함.

#### 1. 실수를 이진수으로 표기

우선 고정소수점 표기법으로 실수를 이진수로 표기하고, 2의 거듭제곱을 곱한 형태(shift)로 나타내 *binary point*를 가장 높은 자릿수의 바로 오른쪽으로 이동시킴. 이후 부호를 부호 비트에, 2의 지수부를 이진수로 나타내 exponent에, mantissa에 최상위 비트부터 가수부를 채워 넣음.

예를 들어, 228(1110 0100)을  $1.11001 \times 2^7$ 로 나타내고, sign bit이 0, exponent이 111, mantissa이 111001000...0을 넣음.

#### 2. mantissa의 최상위 비트 생략

*binary point*를 가장 높은 자릿수의 바로 오른쪽으로 이동시키므로, mantissa에 저장되는 최상위 비트는 항상 1임. 이때의 1을 *leading 1*이라고 함. 1을 작성하지 않고 1이 항상 존재하는 것으로 취급하여 1비트를 아낄 수 있음. 즉, 소수점 아래 부분만을 mantissa에 작성함. 이렇게 *leading 1*을 제외하면 이 부분을 fraction이라고 함. 이때 fraction은 왼쪽(높은 주소 방향)부터 넣음.

예를 들어, 111001000...0을 넣는 대신 110010000...0을 넣음.

#### 3. Biased Exponent 사용

빠르고 간단한 비교와 연산을 위해 *bias*라는 개념을 사용함. *bias*는 양수 값과 음수 값을 모두 표현하기 위한 약속된 값임. *exponent* 값에 *bias*를 더한 값을 *exponent*로 작성하는데, 이를 *biased exponent*라고 함. 8비트를 위한 *bias*는 0111 1111임. *exponent*의 비트가  $n$ 개이면,  $n-1$ 개의 1로 채워진 비트와 최상의 비트 0의 조합(총  $n$ 개)으로 *bias*가 결정됨. 당연하게도 *biased exponent*로 저장된 경우 원래의 값을 얻으려면 *bias*만큼을 빼 줘야 함.

예를 들어, *exponent*가 111인 경우 0111 1111을 더한 값인 1000 0110가 *biased exponent*로 *exponent* 자리에 넣음.

정리하면, IEEE 754 단정밀도 부동소수점 표현 방식은 아래의 과정을 거쳐 실수를 표현함.

1. 고정소수점 방식으로 실수를 이진수로 표기함.

2. 부호에 따라 부호 비트를 넣음.

3. *bias exponent*를 넣음.

4. *fraction*을 넣음.

각 기법의 적용 유무에 따라 다른 부동소수점의 표현 방식으로 생각할 수도 있음.

본 필기는 IEEE 754 단정밀도 부동소수점 표현 방식을 기준으로 작성되었음.

### 2.3.3. 부동소수점 rounding

**Definition 23** 값을 특정 값으로 근사시키는 것을 *rounding*이라고 함.

단정밀도와 배정밀도로는 모든 실수를 표현하는 것이 불가능하기 때문에, 숫자가 너무 크면 *overflow*

가, 숫자가 너무 작으면 underflow가 일어남. 이에 따라 내부적으로 적절한 rounding이 수행됨.

단순한 올림/버림, 0에 가까운 쪽으로 올림/버림, 가장 가까운 수로 올림/버림 하는 방법 등이 존재함.

부동소수점에서 수의 정밀도를 나타내는 것은 가수부임. 즉, fraction에 해당하는 비트 수로 나타낼 수 없는 실수에 대해서 rounding이 필요한 것.

예를 들어, 1.100101을 fractional bit를 3개만 쓰도록 rounding한다고 하면, 올림 시에는 1.101, 내림 시에는 1.100, 0에 가까운 쪽으로는 1.100, 가장 가까운 수로는 1.101로 rounding됨.

### 2.3.4. 정규화된 수와 비정규화된 수

**Definition 24** (biased) exponent가 000...0, 111...1이 아닌 일반적인 경우의 부동소수점 표현은 정규화되어(normalized) 있음. 지금까지 살펴본 표현 방식은 정규화된 수(normalized value)를 나타내는 방식임.

(biased) exponent가 000...0, 111...1인 경우는 예외적인 상황으로, 비정규화된 수(Subnormalized value)를 표현하도록 약속되어 있음.

exponent가 000...0인 경우에는 fraction이 000...0인지, 000...0이 아닌지에 따라 다르게 취급됨. exponent가 111...1인 경우는 특수한 경우에 대한 표현으로 사용되는데, 이는 뒤에 따로 정리함.

1. exponent가 000...0이고, fraction이 000...0인 경우

0.0으로 취급함. 이때 부호 비트에 따라 +0과 -0이 모두 가능함.

2. exponent가 000...0이고, fraction이 000...0이 아닌 경우

exponent와 mantissa를 특수하게 설정함.

-> 저장된 값으로 실제 값을 나타낼 때 exponent 값은 biased exponent - bias가 아니라 1 - bias로 계산함. 즉, 저장된 exponent 값에 +1한 값을 적용함. 또한 mantissa의 생략된 첫번째 비트 수를 leading 1 대신 0으로 계산함. 즉, 저장된 mantissa에 -1한 값을 적용함.

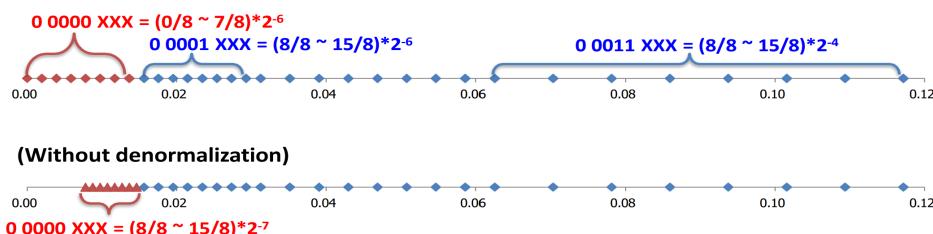

표현 가능한 실수 값을 차례대로 나열해 보면, 각 exponent에 대해 mantissa(fraction)은 항상 균일하게 커지고 작아지는 데에 반해, exponent 값은 2의 거듭제곱으로 적용되므로 그 값이 점점 급격하게 커지고 작아짐. 수직선 상에 표현이 가능한 수들을 찍어 보면 0에 가까워질수록 값이 급격하게 작아져 일부 수들을 표현할 수 없게 됨. 이에 따라 mantissa의 생략된 첫 번째 비트를 0으로 하고 적용되는 exponent 값을 1 크게 함으로써 0과 가까운 각 실수들의 간격을 고르게 할 수 있음. 이를 점진적 underflow(gradual underflow)라고 함.

또한 이런 기법을 적용하면 더 작은 소수까지 표현할 수 있음.

순차적인 값을 비교해 보면 점진적 underflow에 대한 이해가 쉬움. 필요하다면 Number 2 ppt 맨 마지막을 참고하자. 7비트 크기의 부동소수점 표현을 사용한 예시가 있음.

실제로 bias exp가 1인 구간의 mantissa를  $1 + a_1, \dots, 1 + a_n$ 이라고 하고, bias exp가 0인 구간의 mantissa를  $a_1, \dots, a_n$ 이라고 하면 각 구간에서 원소별 간격을 계산할 수 있음. gradual underflow를 적용하면 두 구간 모두 간격이  $(a_{n+1} - a_n) \times 10^{-126}$ 으로 같지만, 적용하지 않은 경우 bias exp가 0인 구간은 간격이  $(a_{n+1} - a_n) \times 10^{-127}$ 이 되어 더 좁음.

### 2.3.5. 특수한 경우에 대한 표현

**Definition 25** 아래와 같이 exponent가 111...1인 경우는 특수한 경우에 대한 표현으로 사용됨.

$\infty$  : 부호 비트가 0, exponent가 111...1, fraction이 000...0.

$-\infty$  : 부호 비트가 1, exponent가 111...1, fraction이 000...0.

$NaN$  : 부호 비트가 0 또는 1, exponent가 111...1, fraction이 0이 아닌 값.

$NaN$ (Not a Number)은 값을 실수로 정의할 수 없음을 나타냄. (ex.  $\sqrt{-1}$ ,  $\log(-5)$ )

### 2.3.6. 부동소수점의 덧셈

부동소수점의 덧셈은 아래의 과정을 거쳐 수행됨.

1. (biased) exponent와 fraction을 추출함.

2. fraction에 leading 1을 추가하여 mantissa로 복원함.

3. exponent가 더 작은 쪽의 mantissa를 시프트하여 두 실수의 exponent를 맞춤.

4. mantissa끼리 덧셈을 수행함.

5. 필요하다면 결과값에서 exponent와 mantissa를 조정해 binary point를 앞으로 당김.

6. exponent/fraction의 비트가 부족할 경우 결과를 rounding함.

7. exponent와 fraction을 부동소수점 format에 삽입함.

복잡한 과정을 거쳐야 하므로 프로세서의 성능 측정 시에 부동소수점 연산을 지표로 사용하기도 하는 것. 연산의 수행을 위해 몇 cycle이 필요함.

### 2.3.7. 부동소수점의 곱셈

부동소수점의 곱셈은 아래의 과정을 거쳐 수행됨.

1. 두 exponent를 더함.

2. 두 mantissa를 곱함.

3. 필요하다면 결과값에서 exponent와 mantissa를 조정해 binary point를 앞으로 당김.

4. exponent/fraction의 비트가 부족할 경우 결과를 rounding함.

5. exponent와 fraction을 부동소수점 format에 삽입함.

덧셈과 곱셈은 비슷한 정도의 시간 복잡도를 가지지만, 곱셈에서는 곱셈 연산이 중간에 수행됨.

### 2.3.8. C에서의 부동소수점

C에서는 float으로 단정밀도 표현을, double로 배정밀도 표현을 지원함.

double, float을 int로 변환 시에는 fraction 부분을 버리는(0쪽으로 rounding하는 것) 과정을 거치고, 반대 변환의 경우에는 주어진 비트 내에서 적절한 rounding을 수행함.

소수의 연산은 표현의 한계 때문에 그 결과가 정확하지 않음. 특히, 연산 시에는 큰 소수끼리 먼저 계산하는 것이 좋음.

참고로, C에서의 자료형 크기는 32비트 os나, 64비트 os나에 따라 달라짐. 다른 자료형들은 크기가 동일한데, long과 포인터 자료형의 크기가 32비트에서는 4바이트이고 64비트에서는 8바이트임.

## Part III

# ISA

## 1. ISA

### 1.1. CPU와 어셈블리어

#### 1.1.1. 어셈블리어

**Definition 26** 어셈블리어는 대체로 하나의 문장이 하나의 기계어와 대응되는 *Low\_level* 언어임.

High\_level 프로그램과 기계어 사이의 Abstraction layer로서 가능함.

기계어는 cpu 종속적이기 때문에, 어셈블리어도 cpu 종속적임.

### 1.1.2. cpu의 구조

**Definition 27** *cpu(Central Processing Unit)*은 아래와 같이 크게 4가지 구성요소를 가지고 있음.

1. *PC(Program Counter)* : 현재 실행 중인 명령어의 주소를 가리키는 레지스터.(제어)

2. 레지스터 파일 : 레지스터.

3. *ALU (Arithmetic/Logic Unit)* : 산술/논리 연산을 수행하는 회로.

4. *Control logic* : *cpu* 동작을 제어하는 부분. *fetch*(명령어 가져옴), *decode*(명령어 해석), *execute*(명령어 실행) 등을 수행함.

현존하는 대부분의 *cpu*들은 이 구조를 따름. *cpu*는 명령어를 순차적으로 실행하고, 내부적으로 다양한 기법들을 사용함.

*cpu*의 작동은 아래 과정의 반복임.

1. *PC*가 가리키는 명령어를 *fetch*

2. *decode*

3. *execute*

4. *update PC*

데이터 이동의 관점에서는 아래 과정의 반복으로도 볼 수 있음.

1. *memory* -> *register*

2. *execute*

3. *register* -> *memory*

## 1.2. ISA

### 1.2.1. ISA

**Definition 28** *ISA(명령어 구조 체계, Instruction Set Architecture)*는 *CPU*가 어떻게 작동하는지에 대한 규격임.

명령어(*instruction set*), 레지스터, 자료형, 주소 지정 방식, 바이트 오더링, 인코딩 방식 등을 포함함.

*isa*는 소프트웨어(os, compiler 등)와 하드웨어 사이의 추상화, 인터페이스로서 가능함. 소프트웨어에서는 하드웨어를 어떻게 조작할지를 생각하고, 하드웨어에서는 소프트웨어의 요구사항에 맞도록 구현하는 것을 생각할 수 있음.

*cpu*마다 각각의 *isa*와 그에 따른 명령어(*instruction set*)를 사용함.

*isa*는 명령어와 그 구조에 대한 설계임. 명령어에 따라 적절한 레지스터가 존재해야 하기 때문에 레지스터에 대한 내용이 포함되어 있고, 명령어가 메모리를 조작해야 하기 때문에 자료형, 메모리 주소 지정 방식, 바이트 오더링, 인코딩 방식 등에 대한 내용이 포함되어 있음.

소프트웨어의 요구사항을 만족하면서 효율적인 하드웨어를 구현하는 *isa*가 이상적임.

### 1.2.2. n비트 ISA

**Definition 29** *n비트 isa라고 할 때 n비트는 명령어 하나를 표현하는 데에 필요한 비트 수임.*

128비트 isa도 존재는 하지만, 현재는 거의 사용되지 않음.

### 1.2.3. 레지스터

**Definition 30** 마이크로프로세서가 사용하는 가장 작고 빠른 메모리를 레지스터(register file)라고 함.

*n비트* 프로세서인 경우 각 레지스터는 *n비트*의 크기를 가짐.

레지스터의 각 비트에 대해 이야기할 때는 *c*의 배열과 같이 0번째~63번째 등으로 표현함.

메모리로의 접근과 레지스터로의 접근은 그 성능 차이가 100배 정도임.

보조기억장치에 있는 코드 등을 메모리에 올리고(프로세스), 메모리의 값을 레지스터로 가져와 산술/논리 연산을 수행함.

이때 메모리는 바이트 단위 주소를 가지고, 코드와 데이터 등을 저장함. 또한 함수 등에 대한 스택이 존재함.

컴파일러는 레지스터 사용을 최적화하여 가능한 한 많은 레지스터를 효율적으로 운용해야 함.

본 수업에서는 기본적으로 64비트 프로세서에 대해 다루고, 그에 따라 레지스터 크기를 64비트로 생각함.

### 1.2.4. isa 디자인 원칙

isa의 연산 디자인에는 몇 가지 원칙이 있음.

1. Simplicity favors regularity(단순함이 규칙성에 유리함)

단순하게 디자인하면 구현을 간단하게 하고, 적은 비용으로 높은 성능을 낼 수 있음.

2. Smaller is faster(작을수록 빠름)

크기가 작아질수록 속도가 빨라짐. 보조기억장치보다 메모리가, 메모리보다 캐시 메모리가, 캐시 메모리보다 레지스터가 빠름. 레지스터의 성능 자체도 더 좋지만, 연산 하나당 가져야 하는 비트 수가 늘어나면 cpu가 처리해야 하는 데이터의 양도 커지므로 속도가 느려짐.

3. Good design demands good compromises(좋은 디자인은 타협을 요구함)

최적화된 설계를 위해 일부 불편함은 감수함. 예를 들어, Instruction format에서 구간을 이상하게 조개는 것은 디코딩 시의 성능 향상을 위한 것임.

4. Make the common case fast (Amdahl's Law)

## 2. RISC-V

### 2.1. RISC-V

#### 2.1.1. RISC-V

**Definition 31** RISC-V는 UC Berkeley에서 개발한 5번째 risc 아키텍처로, RISC-V 아키텍처의 isa는 학계/산업계에서 무료로 이용 가능한 완전 오픈 isa임.

명령어의 길이에 따라 RV32I(RISC-V integer), RV64I, RV128I로 기본 integer(정수용) isa가 3개 존재함. RV32E 같이 레지스터의 개수를 16개로 줄인 RV32I의 임베디드 전용 버전도 존재함.

RV32I는 아래와 같이 여러 확장들을 제공함.

*M* : integer Multiply/Divide 제공.

*A* : atomic instructions 제공.

*F* : single-precision floating point(단정밀도 부동소수점) 제공.

*D* : double-precision floating point(비정밀도 부동소수점) 제공.

*G* : general purpose. IMAFD가 적용됨.

*Q* : quad-precision floating point 제공.

*C* : compressed instructions. 명령어의 길이를 16비트로 줄인 버전. 이는 32비트 명령어와 호환됨.

M extension에는 mul(곱셈) 연산 등이 존재함.

RV32I에는 47개의 명령어들이 존재하는데, x86은 1503개, arm은 500정도인 것을 생각하면 47개는 굉장히 적은 것임. arm은 risc이지만 RISC-V에 비하면 risc에 덜 가까움.

compressed instruction들을 제공하는 C extension과의 호환성을 위해 RV32I는 주소를 2 byte 단위로 alignment 함.

현재 risc 기반 isa는 임베디드에서 자주 사용됨.

본 수업에서는 RV32I를 다룸.

### 2.1.2. RISC-V의 레지스터

RV32I는 아래와 같이 32개의 레지스터들과 pc를 가짐.

| #   | Name  | Usage                                      |

|-----|-------|--------------------------------------------|

| x0  | zero  | Hard-wired zero                            |

| x1  | ra    | Return address                             |

| x2  | sp    | Stack pointer                              |

| x3  | gp    | Global pointer                             |

| x4  | tp    | Thread pointer                             |

| x5  | t0    | Temporaries<br>(Caller-save registers)     |

| x6  | t1    |                                            |

| x7  | t2    |                                            |

| x8  | s0/fp | Saved register / Frame pointer             |

| x9  | s1    | Saved register                             |

| x10 | a0    | Function arguments /<br>Return values      |

| x11 | a1    |                                            |

| x12 | a2    | Function arguments                         |

| x13 | a3    |                                            |

| x14 | a4    |                                            |

| x15 | a5    |                                            |

| x16 | a6    | Function arguments                         |

| x17 | a7    |                                            |

| x18 | s2    | Saved registers<br>(Callee-save registers) |

| x19 | s3    |                                            |

| x20 | s4    |                                            |

| x21 | s5    |                                            |

| x22 | s6    |                                            |

| x23 | s7    |                                            |

| x24 | s8    |                                            |

| x25 | s9    |                                            |

| x26 | s10   |                                            |

| x27 | s11   |                                            |

| x28 | t3    | Temporaries<br>(Caller-save registers)     |

| x29 | t4    |                                            |

| x30 | t5    |                                            |

| x31 | t6    |                                            |

|     |       | pc Program counter                         |

zero는 항상 0(Hard-wired zero)을 저장하고 있는 레지스터로, 값을 수정할 수 없음. 0을 사용 시에 사용함.

ra에는 호출 종료 후 제어가 복귀할 주소를 저장함.

sp에는 현재 스택의 어떤 위치를 사용 중인지 저장함.

s0~s11은 호출된 함수들이 사용하는 레지스터임.

t0~t6는 임시 레지스터로, 일시적인 사용 등을 위한 중간 공간으로 사용함.

a0~a7은 함수의 인자로 작성한 값을 저장하는 레지스터임. 인자로 받는 값이 9개 이상이면 값을 메모리에 저장하고 꺼내야 하기 때문에 성능이 급격히 떨어짐. a0과 a1에는 반환값을 저장하는데, 레지스터가 2개인 이유는 각 레지스터가 32비트 크기이기 때문에 64비트 크기의 데이터를 반환할 때 a0와 a1 모두를 사용해야 하기 때문임.

gp, tp는 이런 것이 있다 정도만 알자.

## 3. RISC-V 연산

레지스터의 값을 이용한 산술/논리 연산, 데이터 이동 연산, 분기 및 호출/반환 연산이 존재함.

연산 시에 레지스터는 최소로 사용하도록 최적화하되는 것으로 보임.

## 3.1. 연산과 데이터

### 3.1.1. 연산의 내부 데이터 구조

RV32I의 연산은 32비트로 표현되고, 각 비트들의 구간은 나름의 역할을 가짐. 이때 각 구간이 가지는 값의 형태는 4가지로 분류할 수 있음.

#### 1. immediate value(상수)

: 자주 사용되는 값을 12비트로 직접 표현해 사용하는 부분. immediate value를 사용하면 상수를 따로 레지스터를 저장하여 사용하지 않아도 됨.

immediate는 signed임.

#### 2. register

: 레지스터 주소.

각 레지스터는 명령어 수행 시에 임시 변수(automatic variable)로 사용되기도 함.

#### 3. memory address

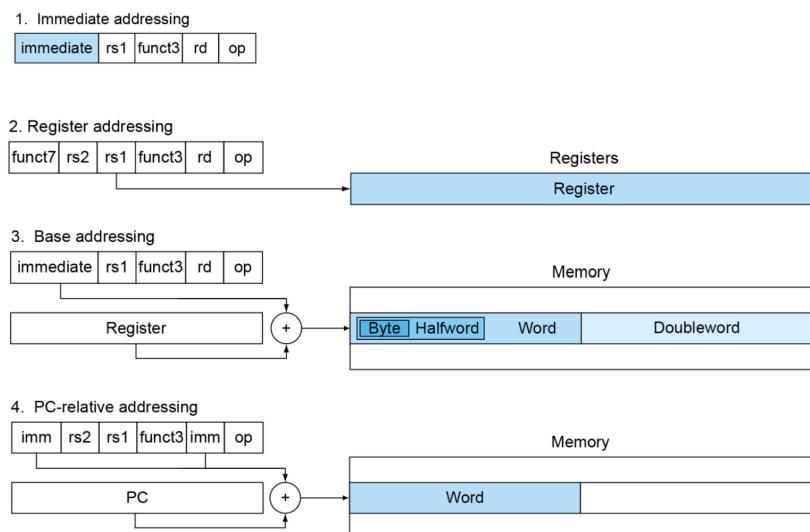

: 레지스터의 값과 immediate 값을 더한 값으로 메모리에 접근함.

#### 4. pc address

: pc에 immediate를 더한 값으로 다음 연산에 접근/분기 등을 함.

### 3.1.2. 데이터 표현 단위

비트는 0과 1을 값으로 가지고, 이런 비트들의 집합으로 byte(8bits), half-word(16bits), word(32bits), double word(64bits)를 만듦.

32비트 크기의 데이터는 워드, 64비트 크기의 데이터는 double word라고 함.

기본적으로 integer(int)는 word의 크기(4바이트)를 가짐.

### 3.1.3. 바이트 오더링

**Definition 32** 바이트 오더링에는 빅 엔디안과 리틀 엔디안이 존재함. 말 그대로 빅 엔디안은 높은 자릿수의 값이 끝(낮은 주소)에, 리틀 엔디안은 낮은 자릿수의 값이 끝에 들어가는 것을 말함.

대부분의 아키텍처가 리틀 엔디안 방식을 따르고, RISC-V에서도 기본적으로는 리틀 엔디안 방식을 지원함.

서로 다른 바이트 오더링을 따르는 시스템 사이의 데이터 이동 시에는 문제가 발생할 수 있음.

Sun, PowerPC Mac, 네트워크 등에서는 빅 엔디안을, intel x86, ARM(Android, ios), RISC-V에서는 리틀 엔디안을 따름.

### 3.1.4. alignment

**Definition 33** 메모리에 저장되는 데이터가 word 등을 기준으로 정렬되도록 하는 것을 *alignment*라고 함.

*alignment*를 하는 것은 메모리를 더 소비하지만 성능적 측면에서는 더 뛰어남. *unaligned*를 사용하면 해당 데이터를 처리하는 데에 시간이 더 오래 걸리고, *atomicity*(원자성)가 부족해 미묘한 버그들이 발생할 수 있음.

RISC-V는 *alignment*를 강제하지는 않지만 성능적 문제로 인해 지키도록 권고함.

alignment를 강제하는 아키텍처에서는 반드시 지켜야 하지만, 초기의 아키텍처들에서 강제되던 alignment는 개발자에게 불편하다는 이유로 사라졌음. 현재는 RISC 등에서 성능을 위해 이를 일부 채택했음.

RISC-V는 *alignment*를 강제하지는 않지만, *alignment*만 지원하도록 설계되어 있고 *unaligned*의 처리에 대해서는 OS의 도움을 추가로 받아야 함.

어떤 한 작업에 대한 연산이 여러 개로 쪼개졌을 때 모든 연산이 전부 통일성 있게 수행되어 하는데, 이를 *atomic*하게 연산이 수행되야 한다고 함. *alignment*가 맞지 않아 연산이 여러 개로 쪼개진 경우 모든 연산을 *atomic*하게 수행하기 힘들기 때문에 버그들이 발생하는 것임.

## 3.2. 산술/논리 연산

### 3.2.1. 산술 연산

**Definition 34** 산술(arithmetic) 연산으로는 아래와 같은 것들이 있음.

*add* : 덧셈.

*sub* : 뺄셈.

*slt* : set less than. (<) 참이면 1, 거짓이면 0을 대입.

*sltu* : 비교하는 피연산자들을 *unsigned*로 취급해 *slt*를 연산함.

RV32I의 모든 산술 연산은 아래와 같이 3개의 피연산자를 가짐. 뒤의 두 피연산자를 연산하여 맨 앞 피연산자에 대입하는 것. 표준 문서 등에 작성할 때 맨 앞 피연산자는 *rd*(register destination), 나머지 피연산자는 *rs*(register source)로 표기하기도 함.

피연산자에 *immediate value*(상수)가 존재하는 연산을 *immediate operands*라고 함. *immediate*값은 주로 *rs2* 자리에 작성함. *immediate operands*는 *addi*와 *subi*와 같이 뒤에 *i*가 붙은 연산을 사용함. 참고로, *sltu*의 *immediate operands*는 *sltiu*로 작성함. *u*가 더 늦게 붙음.

```

add rd, rs1, rs2          // rd = rs1 + rs2

addi rd, rs1, imm12        // rd = rs1 + imm12

slt rd, r1, r2             // r1 < r2으로 rd에 1 또는 0 대입

```

### 3.2.2. upper immediate operation

**Definition 35** *upper immediate operation*은 12비트보다 더 큰 범위의 *immediate*를 사용하기 위한 산술 연산으로, 기존 *immediate*에 해당하는 12비트의 상위 위치에 20비트 *immediate*를 추가로 지정함.

연산으로 지정한 20비트 *immediate*는 레지스터의 12번째~31번째 비트에 들어가고, 기존 *immediate*로 값을 넣을 수 있는 부분인 0번째~11번째 비트는 0으로 채워짐. 또한 64비트 레지스터 기준 32번째~63번째 비트는 *sign extension*하여 31번째 비트 값으로 채움.

*upper immediate operation*으로 아래와 같은 것들이 있음.

*lui* : load upper immediate.

*auipc* : add upper immediate to pc.

아래와 같이 작성함.

```

lui rd, imm20

```

```

auiopc rd, imm20

```

upper immediate operand는 12번째 비트부터 20비트를 채우기 때문에, 아래와 같이 실제로는 addi 등과 함께 사용함. 기존의 연산에서 immediate값이 12비트를 넘어가면 넘어간 만큼을 upper immediate operand로 채워주는 것.

```

lui x19, 0x003D0

addi x19, x19, 0x500 // 결과적으로 0x003D0500이 x19 레지스터에 들어감.

```

|                      |                     |                     |                          |                |

|----------------------|---------------------|---------------------|--------------------------|----------------|

| lui x19, 0x003D0     | 0000 0000 0000 0000 | 0000 0000 0000 0000 | 0000 0000 0011 1101 0000 | 0000 0000 0000 |

| addi x19, x19, 0x500 | 0000 0000 0000 0000 | 0000 0000 0000 0000 | 0000 0000 0011 1101 0000 | 0101 0000 0000 |

### 3.2.3. 논리 연산

**Definition 36** 논리(logical) 연산으로는 아래와 같은 것들이 있음. 전부 비트 단위 연산이고, 동일한 형태로 작성함.

*sll* : shift left logical. 빈 공간은 0을 채움.

*sra* : shift right arithmetic. 빈 공간은 MSB로 채움.

*srl* : shift right logical. 빈 공간은 0을 채움.

*and* : and bit 연산.

*or* : or bit 연산.

*xor* : xor bit 연산.

RV32I의 논리 연산은 아래와 같이 3개의 피연산자를 가짐. 뒤의 두 피연산자를 연산하여 맨 앞 피연산자에 대입하는 것.

논리 연산에도 immediate operands가 존재함. 연산 뒤에 *i*만 붙이면 됨.

```

sll rd, rs1, rs2 // rd = rs1 + rs2

slli rd, rs1, imm12 // rd = rs1 + imm12

```

RISC-V에는 곱셈/나눗셈 연산이 따로 존재하지 않아 시프트/덧셈/뺄셈 연산 등으로 이를 수행함.

and, or, xor 사용 예시로는, and 연산으로는 마스킹하여 특정 비트를 추출/삽입하는 데 사용할 수 있고, or 연산으로는 두 데이터 사이의 포함관계를 판단하는 데에 사용할 수 있고, xor 연산으로 두 데이터가 동일한지를 판단할 수 있음.

참고로 C에서 »는, unsinged 정수형에 대해서는 logical right shift 연산을 수행하고, signed 정수형에 대해서는 arithmetic right shift 연산을 수행함. 부호 비트가 존재하면 반영해 주는 것.

시프트 연산으로 곱셈을 수행하는 예시로, x5에 48을 곱하는 경우 아래와 같이 연산을 수행함.

```

slli x6, x5, 1 // 곱하기 2

add x6, x6, x5 // 원래의 수 더하기

slli x5, x6, 4 // 곱하기 16

```

### 3.2.4. 포인터 vs 배열

C문법 기준으로, 코드 작성 시에는 배열이 포인터보다 편리하지만 실제 수행되는 작업량은 배열이 더 많아 비효율적임.

배열의 경우 요소 크기만큼의 곱셈(시프트)을 해 주고, 배열의 시작 주소에 해당 값만큼 더해 각 요소에 접근함. 반면에 포인터는 단순히 지정한 주소로 이동함.

컴파일 시에 -O1 옵션을 지정하면 배열을 사용해도 포인터와 동일한 연산이 수행됨. 임베디드 시스템 등을 다룰 때는 이런 옵션으로 인해 잘못된 동작이 발생할 수 있긴 함.

배열 인덱스 지정 시에 곱셈 연산 대신 더 효율적인 시프트 연산을 주로 사용함.

### 3.3. 데이터 이동 연산

load와 store는 사용법이 거의 동일함.

#### 3.3.1. load 연산

**Definition 37** 메모리의 데이터를 레지스터로 이동하는 연산으로는 아래와 같은 것들이 있음. 전부 동일한 형태로 작성함.

*ld* : load double word.(64비트)

*lw* : load word.(32비트)

*lh* : load half word.(16비트)

*lb* : load byte.(8비트)

*ldu*, *lwu*, *lhu*, *lbu*와 같이 연산 뒤에 *u*를 붙이면 *unsigned*에 대한 연산이 수행됨. 32비트 레지스터에 값 을 가져올 때 데이터가 *signed*인지 *unsigned*인지에 따라 남은 공간에 *sign extension*을 수행할 것인지를 정하는 것.

*load* 연산의 피연산자는 *destination register*, *base register(address)*, 그리고 *immediate(상수)* *offset*가 존재함. *base register*부터 *offset*만큼의 위치에서 연산 만큼의(word 등) 데이터를 *destination register*로 가져오는 것.

```

lw dst, off(base)

ld rd, imm12(rs1)

```

배열, 구조체, 동적 메모리 등은 그 값을 연산 전에 메모리에서 레지스터로 load해야 함.

#### 3.3.2. store 연산

**Definition 38** 레지스터의 데이터를 메모리로 이동하는 연산으로는 아래와 같은 것들이 있음. 전부 동일한 형태로 작성함.

*sd* : load double word.(64비트)

*sw* : load word.(32비트)

*sh* : load half word.(16비트)

*sb* : load byte.(8비트)

*store* 연산의 피연산자는 *destination register*, *base register(address)*, 그리고 *immediate(상수)* *offset*가 존재함. *destination register*의 데이터를 *base register*부터 *offset*만큼의 위치에 저장하는 것.

```

sw dst, off(base)

sd rd, imm12(rs1)

```

store는 주어진 레지스터 값을 메모리에 그대로 옮겨적기 때문에 *unsigned* 연산이 존재하지 않음.

### 3.4. 분기 연산

#### 3.4.1. 조건부 연산

**Definition 39** 조건이 참이면 분기하는 조건부 연산으로는 아래와 같은 것들이 있음. 전부 *b(branch)*로 시작하고, 동일한 형태로 작성함.

*beq* : branch if equal.(==)

*bne* : branch if not equal.(!=)

*blt* : branch if less than.(<)

```

bgt : branch if greater than.(>)

ble : branch if less than or equal.(<=)

bge : branch if greater than or equal.(>=)

```

조건부 연산은 앞에 작성하는 두 개의 피연산자를 비교하여 참이면 맨 뒤의 *label*로 분기함. 이때 *label*은 이동할 지점을 나타내고, 기계어로 번역 시 주소로 변환됨. *label*에는 12비트 *immediate*를 작성할 수 있는데, 이 경우 *immediate* 만큼이 *pc*에 더해짐.

*bequ, bneu, bltu, bgeu*와 같이 연산 뒤에 *u*를 붙이면 피연산자들을 *unsigned*로 취급해서 연산함.

```

beq rs1, rs2, imm12      // 참이면 pc += SignExt(imm12 << 1)

bltu rs1, rs2, imm12

```

*u*를 붙일 경우, *signed*로 보냐 *unsigned*로 보냐에 따라 엄청 큰 수가 되거나 음수가 되기 때문에 유의해야 함.

### 3.4.2. 무조건 분기 연산

**Definition 40** 무조건 분기하는 연산으로는 아래와 같은 것들이 있음. 전부 *j(jump)*로 시작함. 이 연산들은 프로시저 호출 시에 주로 사용함.

*jal* : jump and link. 지정한 *immediate* 값으로 분기.

*jalr* : jump and link register. 특정 레지스터의 주소로부터 *immediate*만큼 떨어진 위치로 분기. 이런 분기를 *computed jump*라고 함.

*jal*과 *jalr*은 아래와 같은 형태로 작성함. *jal*은 *rd*에 호출 이후 실행할 다음 명령어를 작성하고(*pc + 4* 등) *label*(*pc + imm20*)로 분기함. *jalr*은 *rd*에 호출 이후 실행할 다음 명령어를 작성하고(*pc + 4, x0* 등) *rs1*으로부터 *imm12*만큼 이동한 위치로 분기함.

```

jal rd, imm20

jalr rd, imm12(rs1)

```

함수 호출 시에는 *jal*을, 반환 시에는 *jalr*을 사용함. *jal*로는 *x1(ra)*에 다음 명령어 주소를 작성하고 타겟 주소(*label* 등)로 분기함. *jalr*로는 0x(hard-wired zero)에 주소를 작성하고(*x0*은 수정될 수 없으므로 무시됨.) *x1(ra)*로부터 0만큼 떨어진 위치로 분기함. 즉, 아래와 같이 작성함.

```

jal ra, func      // func 호출

jalr x0, 0(ra)    // 반환

```

*lui*와 *jalr*을 함께 사용하면 총 32비트로 떨어진 위치를 지정할 수 있으므로, *jal*의 20비트로 표현이 불가능한 부분도 표현이 가능함. 아래와 같이 *lui*로 레지스터에 20비트 *upper immediate*를 넣고, 그 값을 *jalr*로 지정한 12비트 *immediate*를 더해 해당 위치로 이동하는 것.

```

lui x19, 0xABCD     // 0xABCD0000이 저장됨

jalr 0x, 0xEFG     // 0xABCD0EFG로 분기됨

```

### 3.4.3. 분기 주소 지정 방식

분기하여 이동할 위치의 주소 지정에는 3가지 특징이 있음. 이때 분기하여 이동하는 지점은 메모리 내의 특정 명령어임.

1. 분기할 위치에 대한 주소는 짹수임.

즉, 2바이트로 alignment가 됨.

RISC-V의 extension 중 c(compressed)에서는 명령어가 16비트 길이로 인코딩되기 때문에, 호환성을 위해 2바이트 단위로 alignment하는 것.

2. 조건부 분기문 주소 지정 방식

branch 시에는 *pc*에 12비트 *immediate*만큼을 더한 주소를 사용함.

if/for/while 등의 branch문에서는 대체로 분기할 주소가 분기 명령어 근처에 존재하기 때문.

### 3. 무조건 분기문 주소 지정 방식

jump 시에는 pc에 20비트 immediate만큼을 더한 주소를 사용함.

jump는 비교적 더 먼 위치로 이동하기 때문에 20비트만큼을 사용하는데, 이때의 20비트는 upper immediate에서의 20비트인 것은 아님. 20비트는 그냥 정해진 크기인 것.

더 먼 거리로 분기해야 하는 경우에 upper immediate를 써서 총 32비트 immediate를 사용함. 이때 lui로 12~31비트를 지정하고 jalr로 0~11비트를 지정해 분기함.

## 3.5. Pseudo-instructions

### 3.5.1. Pseudo-instructions

**Definition 41** 실제로 구현되어 있는 연산은 아니지만, 어셈블리어를 보는 사람의 편의를 위해서 *RV32I*에 정의되어 있는 연산들을 *Pseudo-instructions*라고 함.

사용자에게는 Pseudo-instruction으로 보이지만, 실제로는 대응되는 다른 연산으로 구현이 됨.

Pseudo-instructions로는 아래와 같은 것들이 있음.

| Pseudo-instruction    | Base instruction(s)                              | Meaning                                     |

|-----------------------|--------------------------------------------------|---------------------------------------------|

| li rd, imm            | addi rd, x0, imm                                 | Load immediate                              |

| la rd, symbol         | auipc rd, D[31:12]+D[11]<br>addi rd, rd, D[11:0] | Load absolute address where D = symbol - pc |

| mv rd, rs             | addi rd, rs, 0                                   | Copy register                               |

| not rd, rs            | xori rd, rs, -1                                  | One's complement                            |

| neg rd, rs            | sub rd, x0, rs                                   | Two's complement                            |

| bgt{u} rs, rt, offset | blt{u} rt, rs, offset                            | Branch if > (u: unsigned)                   |

| ble{u} rs, rt, offset | bge{u} rt, rs, offset                            | Branch if $\geq$ (u: unsigned)              |

| b{eq ne}z rs, offset  | b{eq ne} rs, x0, offset                          | Branch if $\{ =   \neq \}$                  |

| b{ge lt}z rs, offset  | b{ge lt} rs, x0, offset                          | Branch if $\{ \geq   < \}$                  |

| b{le gt}z rs, offset  | b{ge lt} x0, rs, offset                          | Branch if $\{ \leq   > \}$                  |

| j offset              | jal x0, offset                                   | Unconditional jump                          |

| call offset           | jal ra, offset                                   | Call subroutine (near)                      |

| ret                   | jalr x0, 0(ra)                                   | Return from subroutine                      |

| nop                   | addi x0, x0, 0                                   | No operation                                |

## 4. Instruction format

### 4.1. Immediate의 저장과 적용

#### 4.1.1. Immediate의 저장

format type별로 immediate가 저장되는 형태가 다름. 이때 immediate는 signed 데이터로, 저장 시에 남은 공간은 sign extension됨. 참고로, imm가 12비트보다 커지면, cpu는 두 개의 명령어로 쪼갬. 물론 unsigned에 대해서는 0으로 extension됨.

##### 1. I, S, U type

immediate값으로는 짹수/홀수 모두 사용되고, 어셈블리 명령어에 작성된 immediate 값 그대로가 메모리에 저장됨.

store/load에서도 메모리에 접근하지만 명령어들에 대해 접근하는 것이 아니므로 alignment을 신경쓸 필요가 없음. 2 byte로 alignment되어 있는 것은 명령어들임.

##### 2. SB, UJ type

immediate값은 짹수만이 사용되고(2 byte alignment), 그에 따라 0번째 비트는 항상 1이므로 생략하여 저장함. 이때 저장 방식은 format type에 따라 상이함.

### 4.1.2. Immediate의 적용

instruction에 저장된 immediate값은 사용 시점에 레지스터에 저장되는데(자세한 것은 더 찾아보자), 이때 저장한 방식에 따라 값이 사용됨.

#### 1. I, S, U type

저장된 immediate값을 signed extension한 값이 그대로 사용됨.

I type인 jalr은 특정 주소로 분기하기 때문에 명령어에 작성된 imm12와 레지스터의 값을 더한 것의 0번째 비트를 0으로 바꾼 후 반영됨. jalr x0, 0(ra)등의 사용에서는 분기하는 주소가 짹수이지만 일반적인 경우에서는 주소 값으로 훌수가 지정될 수 있기 때문임.

예를 들어, 명령어에 imm으로 작성되어 있으면  $pc = (R[rs1] + \text{SignExt}(imm)) \& (\sim 1)$ 과 같이 반영됨.

#### 2. SB, UJ type

저장된 immediate값을 1만큼 왼쪽으로 shift하고, 남은 비트는 signed extension한 값이 사용됨. 즉, 어셈블리 명령어에 작성된 값이 그대로 반영되는 것.

예를 들어, 명령어에 imm으로 작성되어 있으면  $PC = PC + \text{SignExt}(imm[12:1] \ll 1)$ 과 같이 반영됨.

## 4.2. Instruction format

### 4.2.1. Instruction format

**Definition 42** RV32I 모든 명령어들의 크기는 32비트(4바이트)이고 format 종류(type)에 따라 나름의 형태를 가지고 있음.

RV32I에는 R, I, S, SB, U, UJ로 총 6개의 format type이 존재함. cpu는 명령어의 funct7, funct3, opcode로 어떤 type의 어떤 연산인지를 판단함. funct3와 funct7은 additional opcode임.

immediate가 조개져 있는 등 각 type의 구성 요소들이 독특한 배열을 가지는 것은 다른 type들과 값의 위치를 맞추기 위해서임. 이를 통해 하드웨어적인 wire를 간단히 연결할 수 있음.

### 4.2.2. R-type

**Definition 43** R-type(Register)은 두 개의 source register와 하나의 destination register가 존재하는 연산들의 format type임.

산술 연산, 논리 연산에 대한 format type임.

아래와 같은 format을 가짐.

| R-type      | 31 0                           |                                                |                                                |                                |                                     |                             |

|-------------|--------------------------------|------------------------------------------------|------------------------------------------------|--------------------------------|-------------------------------------|-----------------------------|

|             | funct7                         | rs2                                            | rs1                                            | funct3                         | rd                                  | opcode                      |

|             | 7 bits<br>additional<br>opcode | 5 bits<br>2 <sup>nd</sup> source<br>register # | 5 bits<br>1 <sup>st</sup> source<br>register # | 3 bits<br>additional<br>opcode | 5 bits<br>destination<br>register # | 7 bits<br>operation<br>code |

| Instruction | Type                           | Example                                        | funct7                                         | funct3                         |                                     | opcode                      |

| add         | R                              | add rd, rs1, rs2                               | 0000000                                        | 000                            |                                     | 0110011                     |

| sub         | R                              | sub rd, rs1, rs2                               | 0100000                                        | 000                            |                                     | 0110011                     |

| sll         | R                              | sll rd, rs1, rs2                               | 0000000                                        | 001                            |                                     | 0110011                     |

| slt         | R                              | slt rd, rs1, rs2                               | 0000000                                        | 010                            |                                     | 0110011                     |

| sltu        | R                              | sltu rd, rs1, rs2                              | 0000000                                        | 011                            |                                     | 0110011                     |

| xor         | R                              | xor rd, rs1, rs2                               | 0000000                                        | 100                            |                                     | 0110011                     |

| srl         | R                              | srl rd, rs1, rs2                               | 0000000                                        | 101                            |                                     | 0110011                     |

| sra         | R                              | sra rd, rs1, rs2                               | 0100000                                        | 101                            |                                     | 0110011                     |

| or          | R                              | or rd, rs1, rs2                                | 0000000                                        | 110                            |                                     | 0110011                     |

| and         | R                              | and rd, rs1, rs2                               | 0000000                                        | 111                            |                                     | 0110011                     |

#### 4.2.3. I-type

**Definition 44** I-type(Immediate)은 하나의 source register와 하나의 destination register, 12비트 immediate가 존재하는 연산들의 format type임.

피연산자나 offset으로 12비트 immediate를 사용하는 산술 연산, 논리 연산, load 연산, jalr에 대한 format type임.

이때 shift 연산(slli, srli, srai)에 대해서는 funct7이 000000 shamt라고 적혀 있는데, 이때 shamt는 shift amount를 말함. 이는 imm[11:0]값의 첫 6비트는 funct7이 들어가고 나머지는 shift 할 양(shamt)이 들어간다는 것임. 한 번에 shift할 수 있는 양은 프로세서의 shift logic에 의해 결정되는데 이 경우 이를 최대 6비트로 제한을 둔 것임.

아래와 같은 format을 가짐.

| I-type                                                                                               |      | 31                   | imm[11:0] | rs1    | funct3  | rd      | 0 | opcode |

|------------------------------------------------------------------------------------------------------|------|----------------------|-----------|--------|---------|---------|---|--------|

| 12 bits<br>constant operand or<br>offset added to base register<br>(two's complement, sign extended) |      |                      |           |        |         |         |   |        |

| 5 bits<br>source or<br>base address                                                                  |      |                      |           |        |         |         |   |        |

| 3 bits<br>additional<br>opcode                                                                       |      |                      |           |        |         |         |   |        |

| 5 bits<br>destination<br>register #                                                                  |      |                      |           |        |         |         |   |        |

| 7 bits<br>operation<br>code                                                                          |      |                      |           |        |         |         |   |        |

| Instruction                                                                                          | Type | Example              | funct7    | funct3 | opcode  |         |   |        |

| addi                                                                                                 | I    | addi rd, rs1, imm12  | -         | 000    | 0010011 |         |   |        |

| slti                                                                                                 | I    | slti rd, rs1, imm12  | -         | 010    | 0010011 |         |   |        |

| sltiu                                                                                                | I    | sltiu rd, rs1, imm12 | -         | 011    | 0010011 |         |   |        |

| xori                                                                                                 | I    | xori rd, rs1, imm12  | -         | 100    | 0010011 |         |   |        |

| ori                                                                                                  | I    | ori rd, rs1, imm12   | -         | 110    | 0010011 |         |   |        |

| andi                                                                                                 | I    | andi rd, rs1, imm12  | -         | 111    | 0010011 |         |   |        |

| slli                                                                                                 | I    | slli rd, rs1, shamt  | 000000    | shamt  | 001     | 0010011 |   |        |

| srli                                                                                                 | I    | srli rd, rs1, shamt  | 000000    | shamt  | 101     | 0010011 |   |        |

| srai                                                                                                 | I    | srai rd, rs1, shamt  | 010000    | shamt  | 101     | 0010011 |   |        |

| lb                                                                                                   | I    | lb rd, imm12(rs1)    | -         | 000    | 0000011 |         |   |        |

| lh                                                                                                   | I    | lh rd, imm12(rs1)    | -         | 001    | 0000011 |         |   |        |

| lw                                                                                                   | I    | lw rd, imm12(rs1)    | -         | 010    | 0000011 |         |   |        |

| ld                                                                                                   | I    | ld rd, imm12(rs1)    | -         | 011    | 0000011 |         |   |        |

| lbu                                                                                                  | I    | lbu rd, imm12(rs1)   | -         | 100    | 0000011 |         |   |        |

| lhu                                                                                                  | I    | lhu rd, imm12(rs1)   | -         | 101    | 0000011 |         |   |        |

| lwu                                                                                                  | I    | lwu rd, imm12(rs1)   | -         | 110    | 0000011 |         |   |        |

| jalr                                                                                                 | I    | jalr rd, imm12(rs1)  | -         | 000    | 1100111 |         |   |        |

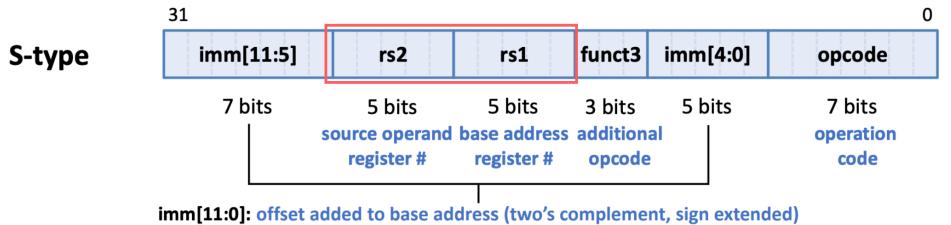

#### 4.2.4. S-type

**Definition 45** S-type(Store)은 두 개의 source register와 12비트 immediate가 존재하는 연산들의 format type임.

offset으로 12비트 immediate를 사용하는 store 연산에 대한 format type임.

I에서는 r1, rd, imm12을 사용했고, S에서는 r1, r2, imm12를 사용함. 다른 format들과의 r1, r2, rd 위치를 맞추기 위해 format type을 분리한 것.

아래와 같은 format을 가짐.

imm[11:0]: offset added to base address (two's complement, sign extended)

#### ▪ Different immediate format for store instructions

- Split so that rs1 and rs2 fields always in the same place

| Instruction | Type | Example            | funct7 | funct3 | opcode                                     |

|-------------|------|--------------------|--------|--------|--------------------------------------------|

| sb          | S    | sb rs2, imm12(rs1) | -      | 000    | 0100011                                    |

| sh          | S    | sh rs2, imm12(rs1) | -      | 001    | 0100011                                    |

| sw          | S    | sw rs2, imm12(rs1) | -      | 010    | 0100011                                    |

| sd          | S    | sd rs2, imm12(rs1) | -      | 011    | Windows 0100011<br>{클정}으로 바탕하여 Windows를 정권 |

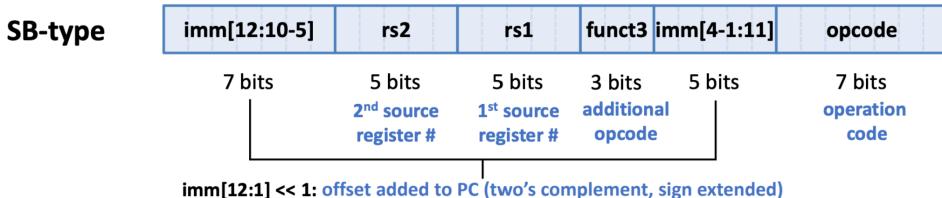

#### 4.2.5. SB-type

**Definition 46** SB-type 또는 B-type(Branch)은 두 개의 source register와 12비트 immediate가 존재하고, 12비트 immediate가 항상 짹수인 연산들의 format type임.

분기할 위치를 짹수 12비트 immediate로 지정하는 조건부 분기 연산(branch)에 대한 format type임.

명령어 상에서 지정한 immediate가 짹수이므로 0번째 비트를 생략한 형태로 저장됨. 기존의 12비트 immediate(0 11번째 존재)에서 13비트까지 Sign Extension을 하고, (부호 비트(MSB)에 해당하는) 11 번째 비트를 0번째 비트 위치에 넣은 형태로 저장함.

아래와 같은 format을 가짐.

imm[12:1] << 1: offset added to PC (two's complement, sign extended)

| Instruction | Type | Example              | funct7 | funct3 | opcode  |

|-------------|------|----------------------|--------|--------|---------|

| beq         | SB   | beq rs1, rs2, imm12  | -      | 000    | 1100011 |

| bne         | SB   | bne rs1, rs2, imm12  | -      | 001    | 1100011 |

| blt         | SB   | blt rs1, rs2, imm12  | -      | 100    | 1100011 |

| bge         | SB   | bge rs1, rs2, imm12  | -      | 101    | 1100011 |

| bltu        | SB   | bltu rs1, rs2, imm12 | -      | 110    | 1100011 |

| bgeu        | SB   | bgeu rs1, rs2, imm12 | -      | 111    | 1100011 |

Windows 정권 안정

예를 들어 1111 1101 0010(이진수)이라는 값을 immeidate로 SB-type 명령어에 저장할 때는, 1111 1101 0011 이 7비트, 5비트로 나누어 들어감.

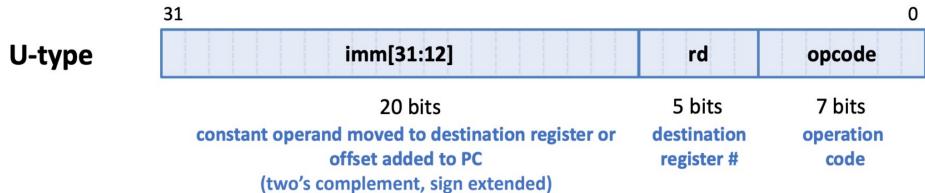

#### 4.2.6. U-type

**Definition 47** U-type(Upper)은 하나의 destination register와 20비트 immediate가 존재하는 연산들의 format type임.

20비트 upper immediate를 지정하는 lui, auipc 연산에 대한 format type임.

아래와 같은 format을 가짐.

- 20-bit immediate is shifted left by 12 bits

| Instruction | Type | Example         | funct7 | funct3 | opcode  |

|-------------|------|-----------------|--------|--------|---------|

| lui         | U    | lui rd, imm20   | -      | -      | 0110111 |

| auipc       | U    | auipc rd, imm20 | -      | -      | 0010111 |

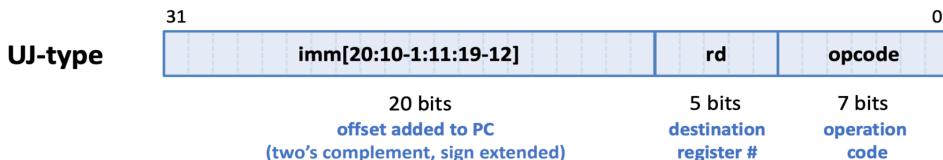

#### 4.2.7. UJ-type

**Definition 48** UJ-type(Unconditional Jump)은 하나의 destination register와 20비트 immediate가 존재하고, 20비트 immediate가 항상 짹수인 연산들의 format type임.

분기할 위치를 짹수 20비트 immediate로 지정하는 jal에 대한 format type임.

명령어 상에서 지정한 immediate가 짹수이므로 0번째 비트를 생략한 형태로 저장됨. 기존의 20비트 immediate(0~19번째 존재)에서 21비트까지 Sign Extension을 한 데이터를 넣음. 부호 비트(MSB)에 해당하는 값을 19번째 비트 위치(맨 앞)에 넣고, 수에 해당하는 부분을 그 다음부터 작성하고, 부호 비트에 해당하는 비트를 바로 다음 비트에 작성하고, 남은 비트들은 부호비트를 Sign Extension한 값으로 채움.

아래와 같은 format을 가짐.

- 20-bit immediate is shifted left by 1 bit and added to PC

| Instruction | Type | Example       | funct7 | funct3 | opcode  |

|-------------|------|---------------|--------|--------|---------|

| jal         | UJ   | jal rd, imm20 | -      | -      | 1101111 |

예를 들어, 0111 1101 0000(이진수)은 0111 1101 0000 0000 0000으로 저장됨.

## 5. 조건문과 반복문

조건문/반복문 등이 RISC-V에서 어떤 어셈블리로 어떻게 구성되어 있는지를 정리함.

기존의 코드를 goto를 사용하는 것으로 바꾸어 놓고 생각하면 더 편함.

## 5.1. 조건문

### 5.1.1. if문

조건이 참인 경우 코드를 건너뛰도록 분기하고, 조건에 맞지 않은 경우 그대로 수행하다가 조건이 참인 경우 분기되는 위치를 만나기 전에 무조건 분기가 되게 함.

이때 무조건 분기는 무조건 분기 연산으로 할 수도 있고, 항상 참인 조건 분기를 사용할 수도 있음.

아래는 그 예시임.

```

// c 코드

if(i == j) f = g + h;

else f = g - h;

// RISC-V 어셈블리어

// i-x22, j-x23, f-x19, g-x20, h-x21

bne x22, x23, L1      // 비교.

add x19, x20, x21      // 참인 경우. f = g + h

beq x0, x0, EXIT        // 참인 경우. 무조건 분기가 됨.

L1:      sub x19, x20, x21  // 거짓인 경우. f = g - h

EXIT:    ...

```

## 5.2. 반복문

### 5.2.1. while문

조건을 검사하여 참이면 Loop label로 분기하고, 거짓이면 Exit label로 분기하도록 함.

while문은 아래의 형태를 가짐.

```

Loop:  참이면 진행, 거짓이면 goto Exit

body

goto Loop

Exit:  ...

```

아래는 그 예시임.

```

// c 코드

while(A[i] == k)

{

i += 1;

}

// RISC-V 어셈블리어

// i-x32, k-x24, A[]-x25, A의 각 요소는 4바이트

Loop:  slli x10, x32, 2      // 조건 검사. i * 4. A의 요소 크기만큼 곱해줌.

add x10, x10, x25      // 조건 검사. 가리킬 주소 지정.

lw x9, 0(x10)          // 조건 검사. load.

bne x9, x24, Exit      // 조건 검사.

addi x32, x32, 1        // 작업.

beq x0, x0, Loop        // Loop로 분기.

Exit:  ...

```

### 5.2.2. do-while문

while과 동일한데, 조건 검사를 맨 마지막에 하면 됨.

do-while문은 아래의 형태를 가짐.

```

Loop:    Body

참이면 goto Loop, 거짓이면 그대로 진행

...

```

### 5.2.3. 반복문 변환

컴파일러에 따라 어셈블리를 생성하는 방법에는 차이가 존재하는데, 아래와 같이 for->while->do-while->goto로 변환하여 생각하는 방법도 존재함. 당연하게도 모든 컴파일러에서 모든 경우에 이런 것은 아니므로, 이런 것도 있다 알고 넘어가자.

RISC-V에서도 O<sub>g</sub> 옵션에서는 while을 그대로 생성하지만, O<sub>2</sub> 옵션에서는 while문을 do-while문으로 변환해 생성하기도 함. 이 경우 더 성능이 뛰어나도록 컴파일한 수도 있음.

아래와 같이 변환이 됨.

```

// for문

for(init; test; update)

body;

// while문

init;

while(test)

{

body;

update;

}

// do-while문

init;

if(!test) goto Exit;

do

{

body;

update;

}while(test)

Exit:

// goto문

init;

if(!test) goto Exit;

Loop:

body;

update;

if(test) goto Loop;

Exit:

```

## 6. 프로시저

### 6.1. 프로시저

#### 6.1.1. 프로시저

**Definition 49** 특정 작업을 위해 사용되는 일련의 절차나 코드 블럭을 프로시저(procedure)라고 함.

다른 프로시저를 호출한 프로시저를 *Caller*, 호출당한 프로시저를 *Callee*라고 함. 또한, 다른 프로시저의 호출을 포함하는 프로시저를 *non-leaf* 프로시저, 그렇지 않은 프로시저를 *leaf* 프로시저라고 함.

엄밀히 말하면 함수와 프로시저는 다르지만, 유사한 것으로 생각할 수 있음.

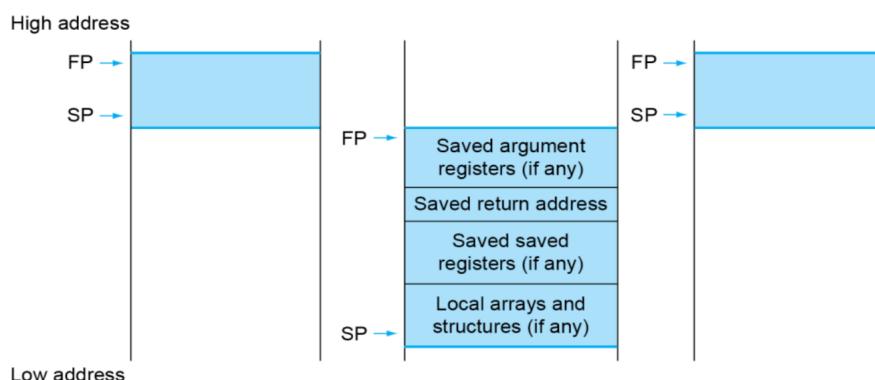

### 6.1.2. RISC-V stack

**Definition 50** RISC-V에서는 프로시저 구현을 위해 메모리 공간에서 LIFO을 따르는 *stack*을 사용함.

*stack*은 거꾸로 자름. 높은 주소를 기준으로 잡아 두고, 해당 주소부터 낮은 주소로 요소를 삽입함. 이때 가장 바깥쪽 요소(*stack*의 *top*)의 주소는  $x2(sp)$ 에 저장함.

RISC-V에는 *push*, *pop* 연산이 존재하지 않기 때문에 *store*, *load*로 스택에서 값을 넣고 꺼냄.

참고로, c/c++, pascal, java 등은 stack 기반 pl(programming language)임. 스택 기반 pl들은 아래의 특징을 가짐.

1. 하나의 프로시저를 여러 번 사용할 수 있음.

프로시저를 인스턴스화하여 재진입이 가능함.

2. 각 인스턴스에 대한 상태를 저장하기 위한 공간을 필요로 함.

3. 프레임으로 스택을 할당함.

### 6.1.3. stack frame

**Definition 51** 프로시저에 대한 정보는 *stack*에 *frame*의 형태로 저장되는데, 이를 *stack frame*이라고 함.

*stack frame*에는 *Caller-saved* 레지스터들(반환 주소, 인자, 지역변수(자동변수), 임시변수 등)이 저장됨.

*frame*의 가장 바깥쪽(낮은 주소)은  $x2(sp)$ 로 가리키고, optional하게 가장 바깥쪽 *frame*의 시작 주소를  $x8(fp, frame pointer)$ 에 저장하기도 함.

*frame*의 생성(할당)에 대한 코드를 *setup code*, *frame*의 삭제(반납)에 대한 코드를 *finish code*라고 함.

stack frame에 데이터를 저장해 둬야 프로시저의 계속된 호출에서도 값을 사용할 수 있음.

### 6.1.4. 인자 전달

인자 전달을 위한 레지스터는 8개 뿐이기 때문에, 이보다 인자가 많이 전달되면 남은 것들은 stack에 역순으로 넣음. 이때 역순으로 넣는 것은 꺼내는 순서를 고려한 것임.

예를 들어,  $arg0 \sim arg9$ 까지 10개의 인자를 전달하려고 하면,  $arg0 \sim arg7$ 은  $a0 \sim a7$ 에 넣고, stack에는  $arg9$ ,  $arg8$  순으로 넣음. 이후에 꺼낼 때  $arg8$ ,  $arg9$  순으로 나오게 하기 위함임.

## 6.2. 프로시저의 구현

### 6.2.1. 프로시저의 구현

**Definition 52** 어셈블리 수준에서 프로시저의 구현을 위해서는 아래의 항목들에 대한 구현이 필요함.

1. *Passing control* : 제어의 이동. 함수 호출과 반환.

2. *Passing data* : 데이터 전달 방식. 인자 값의 전달과 반환값의 전달.

3. *Memory management* : 메모리 관리. 프로시저 실행 동안 할당하고 종료 시 반납.

이에 따라 leaf 프로시저 호출 시 수행되는 작업은 아래와 같음.

1. 프로시저의 인자(argument)는  $x10 \sim x17$  ( $a0 \sim a7$ )에 저장함.

2. 프로시저의 수행 이후 수행할 명령의 주소를  $x1(ra)$ 에 저장하고 프로시저로 분기.

3. 프로시저 수행에 필요한 메모리 공간 확보.

4. *Callee-saved register*를 stack에 삽입/저장.

5. 프로시저의 명령 수행.

6. 반환값을  $a0$ 과  $a1$ 에 저장.

7. *Callee-saved register*를 stack에서 추출/복원.

8.  $x10(a1)$ ,  $x11(a2)$ 에 반환값 지정.

9.  $x1(ra)$ 에 저장된 주소로 이동해 명령 실행.

non-leaf 프로시저의 경우 다른 프로시저를 호출하기 전에 자신의 반환 정보, 인자, 지역변수(자동변수), 임시변수 등을 스택 프레임에 저장함. 이후 다른 프로시저의 수행이 종료되고 제어가 넘어오면 해당 값을 스택 프레임에서 꺼냄.

### 6.2.2. 메모리 공간 확보

프로시저가 호출되면 스택 프레임에 저장할 데이터를 위한 메모리 확보를 함. 그 과정은 아래와 같음.

1. sp 값을 필요한 만큼 증가시킴.

2. stack에 레지스터 값을 store함.

3. 작업 수행.

4. stack에서 레지스터 값을 역순(LIFO)으로 load함.

아래는 그 예시임.

```

// c 코드

int leaf(int g, int h, int i, int j)

{

int f;

f = (g + h) - (i + j);

return f;

}

// RISC-V 어셈블리어

// g-x10, h-x11, i-x12, j-x13

leaf:

addi sp, sp, -8      // 공간 확보

sw x18, 4(sp)        // Callee-save register를 stack에 삽입

sw x19, 0(sp)        // Callee-save register를 stack에 삽입

add x18, x10, x11    // 연산 수행

add x19, x12, x13    // 연산 수행

sub x10, x18, x19    // 연산 수행, 반환값 지정

lw x19, 0(sp)         // Callee-save register를 stack에서 추출

lw x18, 4(sp)         // Callee-save register를 stack에서 추출

subi sp, sp, 8        // 공간 반납

jalr x0, 0(ra)        // 호출된 곳으로 제어 이동

```

### 6.2.3. register saving conventions

**Definition 53** 특정 레지스터들은 그 종류에 따라 저장 규칙이 다름. *Caller-saved* 레지스터인지, *Callee-saved* 레지스터인지에 따라 *Callee*의 해당 레지스터 값 보존 필요 여부가 결정됨.

#### 1. *Caller-saved* 레지스터

: 호출 전에 *Caller*가 그 값을 저장하는 레지스터.  $a0 \sim a7, t0 \sim t6$ .

*Caller*가 저장했으므로 *Callee*의 작업에서 해당 값이 변경되어도 괜찮음.

#### 2. *Callee-saved* 레지스터

: *Callee*가 그 값을 보존해야 하는 레지스터.  $s0 \sim s11$ .

*Caller*가 값을 따로 저장해두지 않았으므로 *Callee*가 해당 값을 보존해야 함. 해당 레지스터에 대한 값의 변경이 예상되면 *Callee* 작업 수행 전에 stack에 그 값을 저장해두고, 이후 반환 전에 원래대로 복구해야 함.

즉,  $s$ 가 붙은(saved)  $s0 \sim s11$ 의 값을 변경하게 되는 경우 stack에 저장했다가 작업 이후에 복원해야 함.

## Part IV

# processor

## 1. datapath

### 1.1. single-cycle processor

#### 1.1.1. execution 과정

명령어 실행의 과정을 더 세분화하면 아래와 같음.

1. Instruction fetch : 메모리에서 processor로 명령어를 가져옴.

2. Instruction decode : 명령어를 디코딩하여 필요한 작업을 지정함.

3. Operand decode : 피연산자(operand)에 해당하는 값을 디코딩하여 가져옴.

4. Execute : 명령어에 해당하는 작업을 수행함.

5. Result store : 결과값을 저장함.

6. Instruction next : 다음으로 수행할 명령어를 정의함.

#### 1.1.2. single-cycle processor

**Definition 54** *single-cycle processor*는 각 명령어의 실행에 하나의 *clock cycle*을 사용하는 processor임. 즉, 각 명령어들이 순차적으로 처리됨.

1. *single-cycle processor*의 장점

로직/클록 등의 구현이 편리함.

2. *single-cycle processor*의 단점

*single-cycle processor*에서는 명령어가 전부 *single-cycle*에 수행되고, 그에 따라 *clock cycle time*이 가장 느린 명령어(critical path)에 의해 결정됨. 이 경우 수행 시간 측면에서 명령어 별 최적화가 되지 않음.

*R-type, load/store, beq* 명령어만이 존재한다고 가정하면, *load*가 *critical path*가 됨.

명령어 별로 사용하는 요소도 있고 사용하지 않는 요소도 있는데, 이게 따른 최적화도 이뤄지지 않음.

즉, *memory*와 *functional unit*의 활용률이 떨어짐.

후술하겠지만 *multi-cycle(pipeline)* processor로 *single-cycle processor*의 단점을 보완할 수 있음. 명령어를 몇 가지 단계로 나누고, 각 단계별로 하나의 cycle을 가지도록 하는 것. 이 경우 *clock cycle time*이 짧아지고, 명령어 별로 다른 CPI를 가지게 됨. 다만, 이를 구현하려면 단계 사이마다 상태를 저장할 레지스터를 추가로 사용해야 함.

각 명령어가 read/write을 positive edge에만 수행할 수 있다면 1 cycle에 명령어 하나가 수행되기 어려우므로, 실제로는 positive edge와 negative edge 모두에서 read/write하는 등 다양한 기법을 사용해 명령어 당 1 cycle을 맞춤.

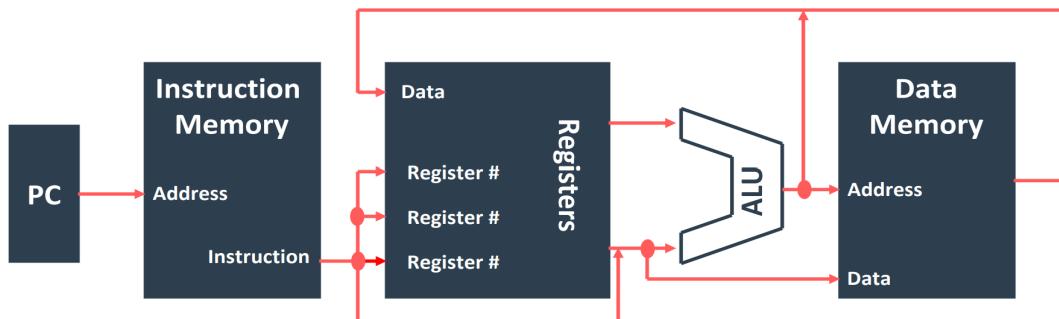

## 1.2. datapath

### 1.2.1. datapath

**Definition 55** *processor(cpu)* 내부에서 명령어를 실행하는 데 사용되는 데이터의 흐름과 제어 신호를 관리하는 *processor(cpu)*의 구성 요소를 *datapath*(datapath)라고 함.

*cpu*는 *datapath*와 *control*로 구성된다고 생각할 수 있음. 물론 *datapath*에는 *RAM* 또한 있으므로 모든 부분이 *cpu*에 포함되는 것은 아님.

여기서는 단순한 구조에 대한 설명을 위해 RV32I의 명령어 중 일부(lw, sw, add, sub, and, or, beq)만을 다룸. 실제로 RV32I의 모든 명령어들을 전부 실행할 수 있는 datapath는 더 복잡한 구조를 가짐.

또한 단순함을 위해 우선 single-cycle processor의 datapath를 확인함.

### 1.2.2. datapath의 기본 구조

단순하게 본다면, datapath는 pc, instruction memory, register file, ALU, data memory로 구성됨.

## 1.3. 디지털 시스템의 구현

물리적인 회로와 신호 등을 통해 디지털 시스템을 구현할 수 있음. RV32I의 datapath에서 디지털 시스템을 구현하는 요소(컴포넌트, component)로는 조합 회로, 순차 회로, 클럭 신호가 있음.

### 1.3.1. 조합 회로

**Definition 56** 조합 회로(combational element)는 논리 게이트들의 비순환형(acyclic) 연결로, *output*이 오직 해당 연산에서의 *input*에 따라 결정되는 회로임.

*input*이 들어오면 지정된 작업이 순차적으로 수행되기 때문에 내부 회로의 복잡도에 따라 어느 정도의 수행 시간이 소요됨(after some delay).

대표적으로 산술(arithmetic)/논리(logical) 연산이 조합 회로로 구성됨. 연산 종류에 따라 AND-gate, Adder, Multiplexer, ALU 등이 존재함.

조합 회로는 연산 종류에 따른 도미노처럼 동작함. 이런 논리 게이트들의 집합을 함수처럼 생각할 수도 있음.

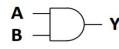

아래와 같이 AND-gate, OR-gate, Adder, Multiplexer, Arithmetic/Logic Unit 등의 조합 회로들이 존재하고, 각 종류에 따른 모양으로 표기함.

■ AND-gate

•  $Y = A \& B$

■ Adder

•  $Y = A + B$

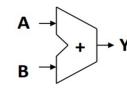

■ Multiplexer

•  $Y = S? A : B$

■ Arithmetic/Logic Unit

•  $Y = F(A, B)$

### 1.3.2. 순차 회로

**Definition 57** 순차 회로(sequential element)는 output이 현재 상태와 input에 의해 결정되는 회로임.

대표적으로 register에 비트 값을 저장(write)하는 회로로 사용됨.

순차 회로는 신호에 의한 차단기처럼 동작함.

### 1.3.3. 레지스터에서의 순차 회로

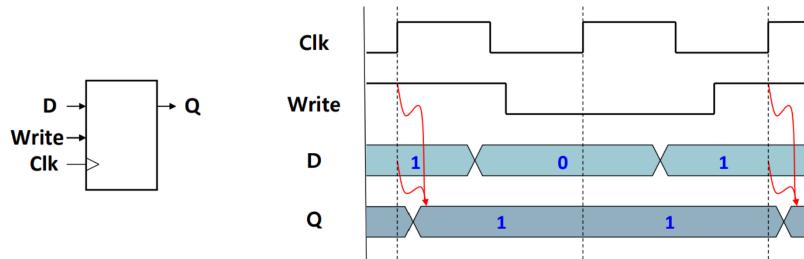

레지스터에서는 clock 신호와 write 신호(control)에 의한 순차 회로로 데이터를 저장함.

레지스터에서 순차 회로를 사용하여 1비트를 저장하는 작업은 다음과 같이 수행됨. 우선 clock 신호는 짐작 박동처럼 계속해서 일정한 주기로 반복됨. 이때 순차 회로는 positive edge마다 write 신호를 확인하는데, 1이면 input값을 output값으로 반영하고 0이면 작업을 수행하지 않음. 이때 신호가 물리적으로 회로를 거쳐야 하기 때문에 input값이 output값으로 반영되는 데에는 시간적 간격(delay)이 존재함.

실제로는 write 뿐만 아니라 read 또한 clock에 맞추어 동작함.

clock은 1과 0이라는 상태보다는 positive/negative edge가 중요함.

## 1.4. datapath의 구성요소

### 1.4.1. datapath의 구성요소

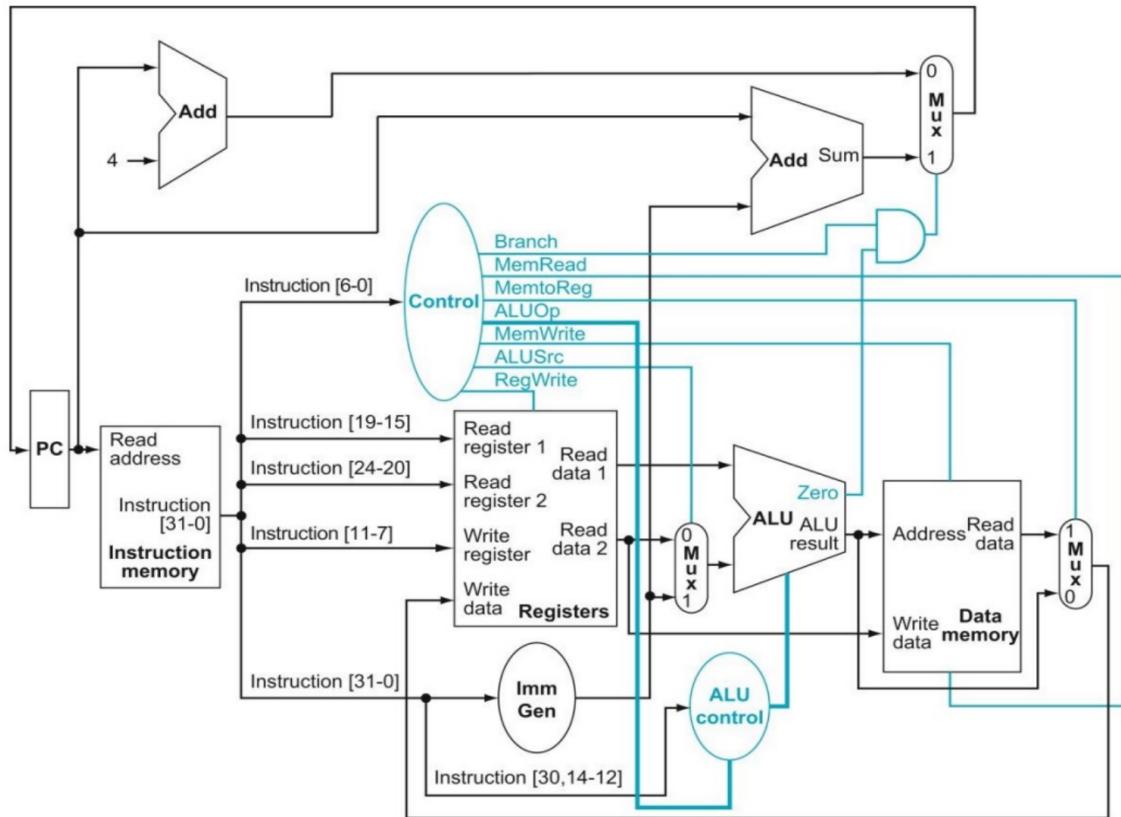

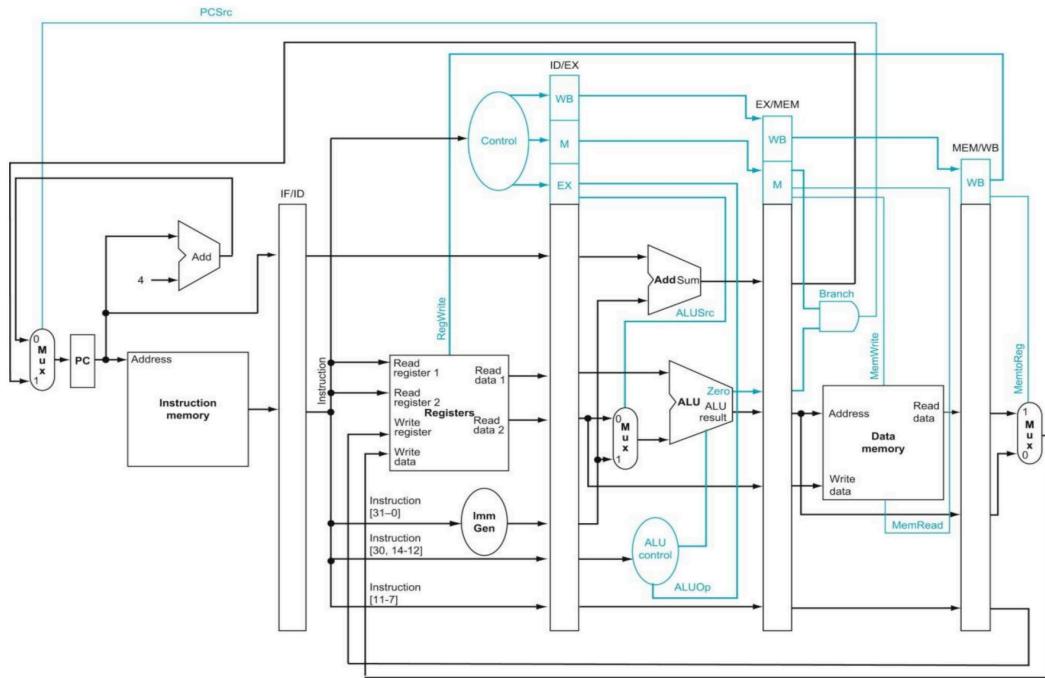

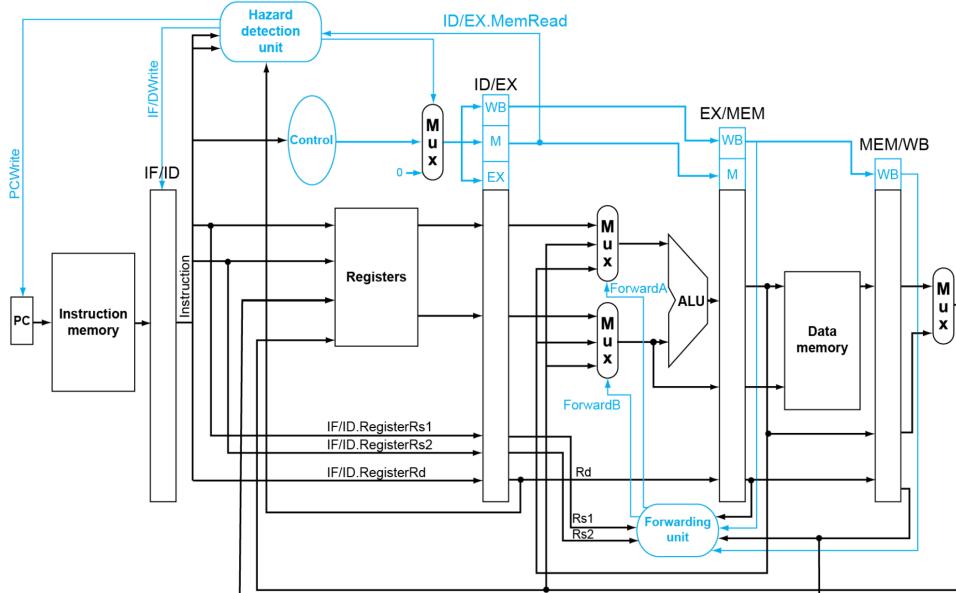

datapath는 아래와 같이 PC, ALU, register file, data memory, instruction memory, add/mux, imm gen 등으로 구성되어 있음. 아래의 그림은 datapath와 control을 함께 나타낸 것임.

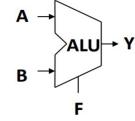

#### 1.4.2. ALU

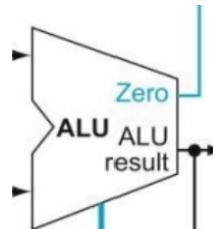

**Definition 58** ALU(Arithmetic/Logic Unit)는 산술/논리 연산을 수행하는 케이트들의 집합임.

control의 ALUOp 신호와 명령어 종류에 따라 ALU control이 ALU에 신호를 보내면, 두 가지 피연산자에 대해 적절한 연산이 선택되어 수행됨.

##### 1. ALU의 연산 수행

load/store의 경우 내부적으로 add 연산( $rs1+imm12$ )이 수행되고, branch(beq)의 경우 내부적으로 sub 연산이 수행되고, R-type의 경우 해당 연산이 수행됨.

##### 2. zero 신호

일반 산술/논리 연산의 경우 연산의 결과가 출력되지만, beq의 경우 내부적으로 sub 연산을 수행하여 그 값이 0이면(같은 경우) zero 신호로 1을, 0이 아니면(다른 경우) zero 신호를 0으로 전송함.

연산 결과가 0이면 zero 신호가 전송되는데, zero 신호와 branch 신호의 AND 연산을 수행하여 출력된 신호를 pc값 지정을 위한 mux에 사용함. 이 mux는 다음에 수행할 명령어에 대한 pc값으로 pc+4을 적용할 것인지, pc+offset을 적용할 것인지를 결정하는 회로임.

load/store, beq 또한 내부적으로는 add와 sub 연산만을 필요로 하기 때문에 ALU로 연산을 수행할 수 있음.

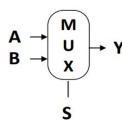

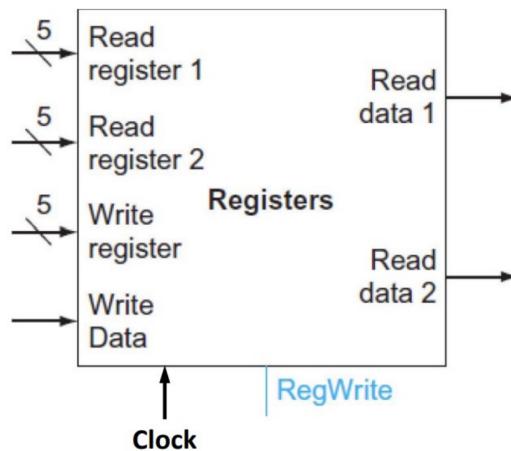

#### 1.4.3. register file

**Definition 59** register file은 register들의 집합이고, 아래의 그림과 같은 구조를 가짐.

1. read/write 포트

register file은 read/write을 위한 복수의 포트들을 가지기 때문에, 한 cycle 내에서 여러 개의 값을 읽고 쓸 수 있음.

RV32I에서 register는 총 32개이므로 register를 지정하는 부분은 5비트 크기의 bus(wire)가 연결되어 있음. Read data 1, 2와 Write data는 32비트 크기의 bus(wire)가 연결되어 있음. 추가로, 0값에는  $x0$ (hard wired zero)가 사용됨.

register의 값을 내보낼 때 read register 1의 값은 read data 1으로, read register 2의 값은 read register 2로 보냄.

write register에는 write을 수행할 register를, write data에는 write할 값이 들어옴.

2. clock/RegWrite 신호

write시에는 순차 회로를 위한 clock 신호와 write 신호가 필요함. 이때 RegWrite 신호가 write 신호로서 가능함. RegWrite이 1이면 해당 register에 데이터가 저장(write)됨.

RegWrite이 0이면 read를 수행하는 것으로, output이 input(register 주소)에 의해 결정되는 조합 회로처럼 동작함. RegWrite이 1이면 write를 수행하는 것으로, 순차 회로로서 동작함.

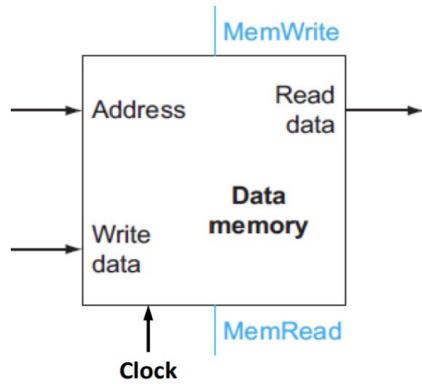

#### 1.4.4. data memory

**Definition 60** data memory는 RAM에서 프로그램 데이터를 저장하기 위한 부분임. 아래의 그림과 같은 구조를 가짐.

register file과 유사한 구조를 가지며 유사하게 동작함. 즉, read 시에는 조합 회로처럼 동작하고 write 시에는 순차 회로로서 동작함. 단, data memory는 read와 write을 위한 MemRead와 MemWrite 신호를 모두 사용함.

일부 명령어(load)만이 data memory에서 데이터를 읽어오므로, 불필요한 read를 수행하지 않기 위해서 MemRead 신호 또한 존재하는 것임.

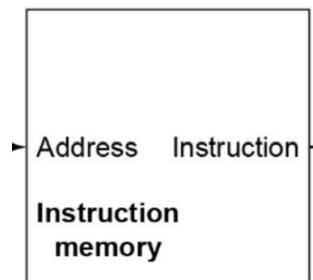

#### 1.4.5. instruction memory

**Definition 61** *instruction memory*는 RAM에서 명령어를 저장하여 읽기 전용으로 사용하는 부분임.

RAM을 *data memory*와 *instruction memory*로 구분한 것은, *instruction*을 *read*하는 작업이 반복해서 수행되어야 하기 때문임.

*instruction memory*는 *read*만 수행하므로 신호가 필요 없음.

#### 1.4.6. multiplexer

**Definition 62** *multiplexer(mux)*는 여러 개의 *input* 신호들을 하나의 *output* 신호로 내보내는 조합회로임.

*mux*를 사용하여 여러 신호가 합쳐지는 부분에서 특정 신호를 선택하여 내보내는데, *control*의 *select* 신호로 어떤 신호를 내보낼지를 결정함. 이를 통해 명령어에 따라 다른 *data source*를 사용할 수 있도록 함.

*mux*에  $2^n$  개의 *input line*이 연결되어 있다면, 특정 신호를 선택하기 위해  $n$ 비트 크기의 *select* 신호가 필요함.

당연하게도 *mux*는 여러 신호를 병합할 때 사용하는 것이지, 하나의 신호를 여러 *line*으로 분리할 때는 사용하지 않음.

#### 1.4.7. imm gen

**Definition 63** *immediate generator unit*은 명령어에서 *immediate*에 해당하는 부분을 가져와 작업에 사용할 원래의 *immediate*를 복원하여 출력하는 요소임.

명령어 인코딩 시에 *sign extend*하여 순서를 뒤바꿔 놓은 것을 원래의 순서로 복원하고, 1만큼 *shift left*하는 등의 과정을 수행함. 물론 *jalr* 등에서는 다른 형태의 과정을 가지겠지만, 여기서는 다루지 않음.

#### 1.4.8. control

**Definition 64** *control*은 명령어에서 *opcode*를 받아, 해당 작업에 필요한 신호를 생성하여 *datapath*의 각 부분으로 보내는 요소임.

*control*은 제어 신호의 유형을 분류해 놓고, *mux*의 신호를 보내 *data* 흐름을 제어하고, 각 요소의 상태를 지정하고, 명령어에 따른 제어를 수행함.

#### 1. *opcode*

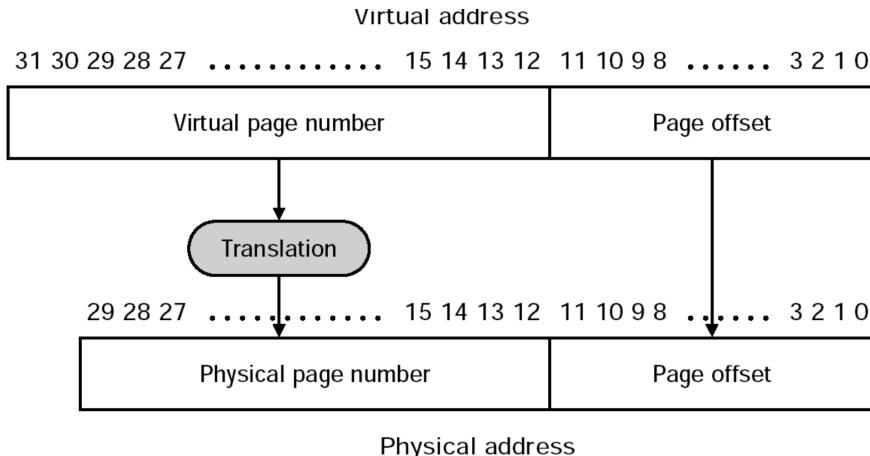

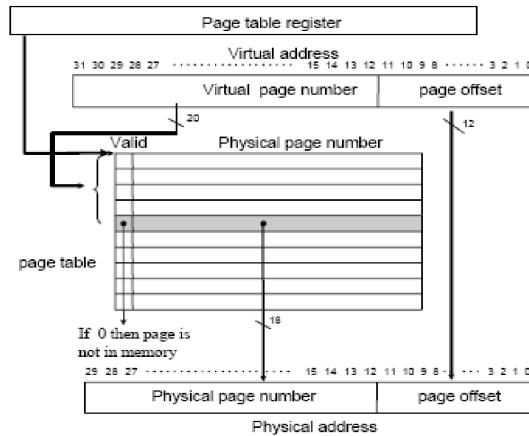

*opcode*는 명령어의 범주에 따라 지정되어 있고, *funct3*와 *funct7*으로 해당 범주 내에서 명령어를 구분함. 이때 이 범주는 *format type*이 아니라 산술/논리 연산, *load* 연산, *store* 연산, *branch* 연산 등 *datapath*에서 명령이 수행되는 형태에 따른 구분임.

그렇기 때문에 *control*은 *opcode*에 해당하는 *instruction[6-0]*으로 해당 명령어에 대한 신호를 각 요소에 전달하여 *datapath*를 제어함.

#### 2. *control*의 신호 전송

*single-cycle*에서 *control*은 아래와 같은 신호들을 전송함.

*RegWrite* : *register*에서의 *write(1)/read(0)* 지정.

*ALUSrc* : *ALU*의 *source*로 들어갈 *rs2(0)/imm(1)*를 지정.

*ALUOp* : *ALU*에서 수행할 연산 지정.

*MemWrite* : *data memory*에서의 *write(1)* 지정.

*MemRead* : *data memory*에서의 *read(1)* 지정.

*MemtoReg* : *register*의 *Write data*로 들어갈 *ALU*의 연산 결과(0) 또는 *data memory(1)* 값을 지정.

*PCSrc* : *pc*를 *update*할 *pc+4(0)/pc+imm(1)*를 지정. *branch*와 *zero*에 대한 *AND* 연산으로 표기하기도 함.

*branch* : 현재 명령이 *branch* 명령어인지(1) 지정.

각 신호들 중에 해당 명령어에서 사용되지 않는 신호는 어떤 값을 가지더라도 상관 없기 때문에 *don't care*라고 부름. 이때 *don't care*는 0/1이 아니라 X임. 물론 *don't care*는 기본적으로 0으로 지정하여 안정성을 높임.

#### 3. *ALUOp*

현재 상황에서 *ALUOp*는 (4가지 연산이므로) 아래와 같이 2비트 크기로 나타낼 수 있음. *ALU control*에는 *funct3*, *funct7*이 전달되므로 이후 구체적으로 연산이 지정됨.

00 : *lw, sw* (*add* 수행)

01 : *beq*

10 : *R-type*

### 1.4.9. *ALU control*

**Definition 65** *ALU control*은 *control*과 분리되어 *ALU*가 수행할 연산을 지정하는 요소임.

#### 1. *ALU control*의 신호 전송

*ALU control*은 *control*로부터 *ALUOp* 신호와, *instruction*의 [30, 14-12] 부분으로 어떤 연산을 수행할지를 결정하는 신호를 *ALU*에 보냄.

현재 상황에서 *ALU*에 전달되는 *data*는 아래와 같이 4비트 크기로 각 연산을 지정할 수 있음.

0000 : *AND*

0001 : *OR*

0010 : *add*

0011 : *sub*

#### 2. *ALUOp, funct3, funct7*

*ALU control*은 *ALUOp*와 *funct7*, *funct3*에 해당하는 *instruction[30, 14-12]*를 읽어 *ALU*에 신호를 보냄. 이때 [14-12]가 *funct3*에 해당하는 부분이고 [30]이 *funct7*에 해당하는 부분임. 잘 보면 *funct7*은 하나의 비트 값만을 사용함.

## 1.5. 명령어 실행 과정

### 1.5.1. pc update(fetch)

pc값을 update할 때는 해당 명령어가 pc값에 +4를 하는 명령어인지, 다른 위치로 분기하는 명령어(branch) 인지에 따라 작업이 수행되어야 함.

pc+4를 수행하는 Adder의 값과, pc+immediate(offset)을 수행하는 Adder의 값을 mux로 선택하여 사용함. 이때 mux의 신호로는 branch 신호와 zero 신호의 AND 연산으로 나온 신호를 사용하는데, pc+immediate(offset)을 적용하는 경우는 branch 명령어에 대해 조건 연산이 참인 경우이기 때문임.

### 1.5.2. R-type 명령어의 실행

R-type은 op rd, rs1, rs2로 구성되어 있으므로, 해당 피연산자들에 대해 적절한 연산이 수행되도록 회로를 생각할 수 있음.

1. pc값에 해당하는 명령어를 instruction memory에서 읽어옴.

2. 명령어의 각 부분이 적절한 요소로 전송됨.

3. register에서 read register 1,2, write register를 모두 입력받고, read data 1,2로 연산할 데이터들을 출력함.

4. rs2값이 연산에 사용되므로 ALUSrc 신호는 0임.

5. 해당 데이터들로 ALU에서 연산을 수행하고, 그 결과를 ALU result로 출력함.

6. MemWrite/MemRead 신호는 모두 0으로 data memory에 접근하지 않음.

7. MemtoReg 신호는 0으로 해당 연산 결과를 바로 register로 보냄.

8. 연산 결과를 write data로 받아서 write register에 해당하는 register에 write함. 이때 RegWrite 신호는 1임.

9. Branch/Zero 신호는 모두 0 이므로 pc값은 pc+4로 update됨.

### 1.5.3. load 명령어의 실행

load 연산(L-type)은 op rd, imm12(rs1)으로 구성되어 있으므로, 해당 피연산자들에 대해 적절한 연산이 수행되도록 회로를 생각할 수 있음.

1. pc값에 해당하는 명령어를 instruction memory에서 읽어옴.

2. 명령어의 각 부분이 적절한 요소로 전송됨.

3. RegWrite가 0으로, register에서 read register 1, write register를 입력받고, read data 1로 연산할 데이터를 출력함.

4. imm값과 연산을 하므로 ALUSrc는 1임.

5. 해당 데이터들로 ALU에서 연산을 수행하고, 그 결과를 ALU result로 출력함.

6. MemWrite 신호는 0, MemRead 신호는 1로, data memory에서 read한 값을 read data로 보냄.

7. MemtoReg 신호는 1로 data memory의 값을 register로 보냄.

8. RegWrite가 1로, data memory의 값을 write data로 받아서 write register에 해당하는 register에 write함.

9. Branch 신호가 0 이므로 pc값은 pc+4로 update됨.

### 1.5.4. store 명령어의 실행

store 연산(S-type)은 op rs2, imm12(rs1)으로 구성되어 있으므로, 해당 피연산자들에 대해 적절한 연산이 수행되도록 회로를 생각할 수 있음.

1. pc값에 해당하는 명령어를 instruction memory에서 읽어옴.

2. 명령어의 각 부분이 적절한 요소로 전송됨.

3. RegWrite가 0으로, register에서 read register 1,2를 입력받고, read data 1,2로 연산할 데이터를 출력함.

4. imm값과 연산을 하므로 ALUSrc는 1임.

5. 해당 데이터들로 ALU에서 연산을 수행하고, 그 결과를 ALU result로 출력함.

6. MemWrite 신호는 1, MemRead 신호는 0로, data memory의 Address에 해당하는 부분에 Write data값을 write함.

7. MemtoReg 신호는 사용되지 않음.

8. Branch 신호가 0 이므로 pc값은 pc+4로 update됨.

### 1.5.5. beq 명령어의 실행

beq 연산(SB-type)은 op rs1, rs2, imm12로 구성되어 있으므로, 해당 피연산자들에 대해 적절한 연산이 수행되도록 회로를 생각할 수 있음.

1. pc값에 해당하는 명령어를 instruction memory에서 읽어옴.

2. 명령어의 각 부분이 적절한 요소로 전송됨.

3. RegWrite가 0으로, register에서 read register 1,2를 입력받고, read data 1,2로 연산할 데이터를 출력함.

4. rs2값이 연산에 사용되므로 ALUSrc 신호는 0임.

5. 해당 데이터들로 ALU에서 sub 연산을 수행하고, 그 결과가 0이면(같으면) zero 신호를 1로, 0이 아니면(다르면) 0으로 함.

6. MemWrite/MemRead 신호는 모두 0으로 data memory에 접근하지 않음.

7. MemtoReg 신호는 사용되지 않음.

8. Branch 신호가 1이므로 zero가 1이면 pc값은 pc+imm12로 update되고, zero가 0이면 pc값은 pc+4로 update됨.

## 2. pipeline

### 2.1. pipeline

#### 2.1.1. pipeline

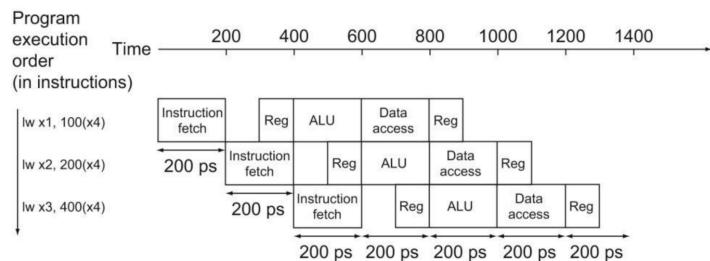

**Definition 66** pipelining은 명령어를 여러 stage로 나누어 datapath의 각 부분에서 해당되는 stage를 계속해서 수행하게 함으로써, 동시에 여러 명령어를 처리하는 것을 말함.

명령어를 순차적으로 처리하는 single-cycle processor에서는 한 번에 하나의 명령어만을 처리할 수 있지만, pipelining을 적용하면 여러 명령어를 동시에 겹쳐서 처리할 수 있음.

당연하게도 pipelining을 통한 성능 향상은 명령어 당 처리 시간을 줄이지는 못하지만, 명령어들에 대한 처리량을 높인 것임.

pipelining은 코어 개수에 대한 이야기가 아니라, 코어 내부에서의 성능을 향상시키는 것.

물론 특정 stage가 필요 없어서 수행하지 않는 명령어에 대해서는 처리 시간이 줄었다고 할 수도 있지만, single-cycle에서도 clock cycle time이 가장 느린 명령어에 맞춰져 있으므로 오래 걸린 것이지 실제로 작업을 수행한 시간은 동일함.

#### 2.1.2. stage

**Definition 67** 명령어 처리 과정은 몇 가지 stage로 뚫어서 분류할 수 있음. risc-V는 기본적으로 five stage pipeline을 사용함.

1. IF(instruction fetch) : memory에서 instruction을 fetch.

2. ID(instruction decode) : instruction decoding, register read.

3. EX(execute) : execute/calculate.

4. MEM(memory) : access memory.

5. WB(write back) : write result back to register.

### 2.1.3. pipeline 성능

**Definition 68** *clock cycle time*은 가장 느린 stage에 맞춰지기 때문에, stage들의 수행 시간이 균일할 수록 pipeline의 성능이 좋음.

stage별 수행 시간에 차이가 크다면, 어떤 stage가 계속 수행되고 있을 때 다른 stage에서는 미리 작업을 끝내고 아무 작업도 하지 않는 시간이 길어짐.

non-pipelined일 때의 실행 시간을 stage 개수로 나눈 것이 각 stage당 걸리는 시간이라면 최적임.

## 2.2. RISC-V pipeline

### 2.2.1. RISC-V으로의 pipelining

**Definition 69** RISC-V isa는 아래의 이유들 때문에 pipelining에 적합함.

1. 명령어 길이가 32bit로 고정되어 있음.

IF, ID에서 수행해야 하는 작업량이 적어 1 cycle 안에 stage를 넣기 쉬움.

길이가 고정되어 있지 않다면 매번 검사하고 길이에 따른 작업을 수행해야 함.

2. 명령어의 format이 제한되어 있고 align되어 있음.

간단하게 설계할 수 있고 작업량이 적음.

3. 주소 지정 방식이 단순함.

주소 계산에 대한 추가적인 stage 대신 단순 ALU 연산으로 이뤄지는 것이 설계에 유리함.

### 2.2.2. pipelined datapath

**Definition 70** pipelining을 하려면 각 stage 별로 다른 명령어에 대한 작업을 수행해야 하므로, stage 직전의 정보를 저장하는 register들이 추가로 필요함. pipeline에 들어가는 추가적인 register를 pipeline register라고 함.

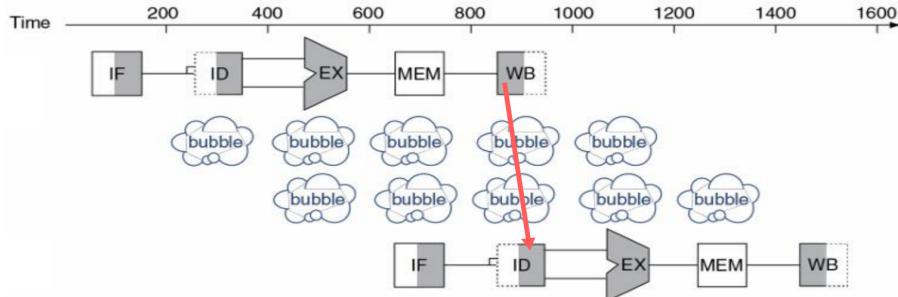

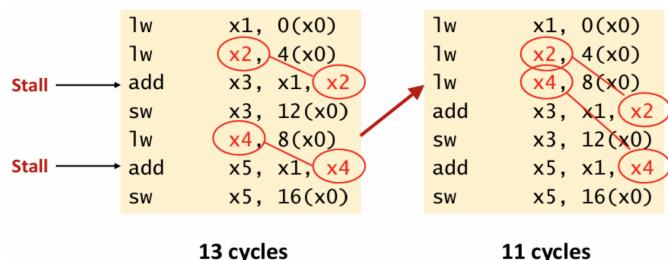

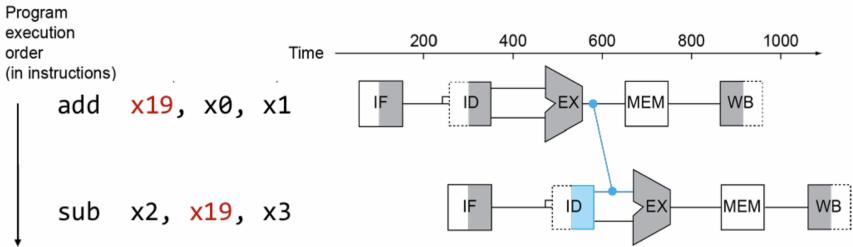

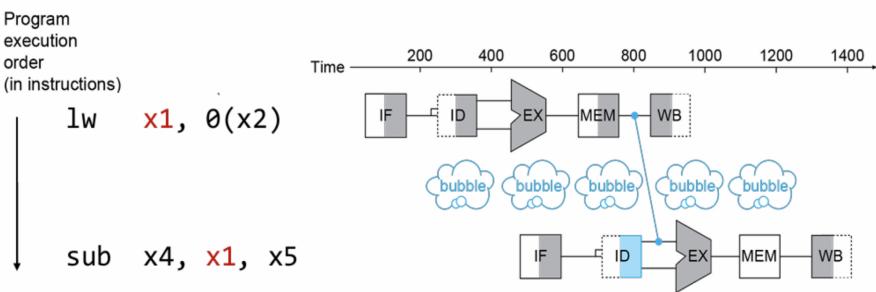

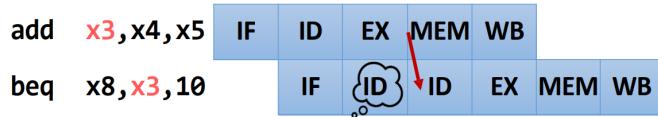

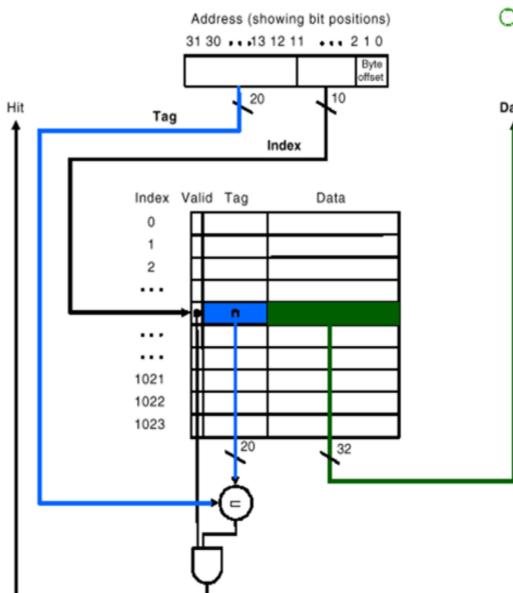

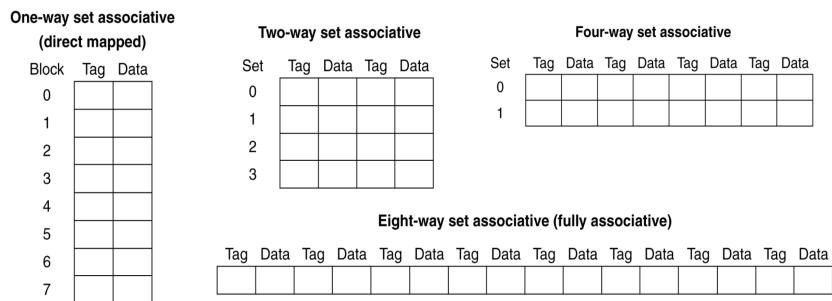

Write Register에 해당하는 값을 Register에 바로 넣으면 다른 명령어와 stage가 겹치게 되므로, Write Register 값을 register에 저장하며 WB까지 가져간 후에 전달해야 함.